# **BAT32A237** Datasheet

Ultra-low-power 32-bit microcontroller based on the ARM® Cortex-M0®+

Built-in 128K bytes Flash, rich analog functions, security functions, timers and various communication interfaces

V1.0.3

Please note the following CMS IP policy

\*Zhongwei Semiconductor (Shenzhen) Co., Ltd. (hereinafter referred to as the Company) has applied for a patent and enjoys absolute legal rights and interests. The patent rights related to the Company's MCUs or other products have not been authorized to be licensed, and any company, organization or individual who infringes the Company's patent rights through improper means will take all possible legal actions to curb the infringer's improper infringement and recover the losses suffered by the Company as a result of the infringement or the illegal benefits obtained by the infringer.

\*The name and logo of Zhongwei Semiconductor (Shenzhen) Co., Ltd. are registered trademarks of the Company.

\*The Company reserves the right to further explain the reliability, functionality and design improvements of the products in the data sheet. However, the Company is not responsible for the use of the Specification Contents. The applications mentioned herein are for illustrative purposes only and the Company does not warrant and does not represent that these applications can be applied without further modification, nor does it recommend that its products be used in places that may cause harm to persons due to malfunction or other reasons. The Company's products are not licensed for lifesaving, life-sustaining devices or systems as critical devices.

## Function

- Ultra-low power operation environment:

- Supply voltage range: 2.0V to 5.5V

- Temperature range: -40°C to 125°C

- Low power mode: sleep mode, deep sleep mode

- Operating power consumption: 120uA/ MHz@48MHz

- Power consumption in deep sleep mode: 0.7uA

- Deep sleep mode +32.768K+RTC operation: 0.8uA

- Kernel:

- ARM®32-bit Cortex-M0®+ CPU with MPU memory protection unit with MTB on-chip tracking unit

- ➢ Working frequency: 32KHz∼48MHz

- Memory:

- 128KB Flash memory, program and data storage sharing

- > 1.5KB dedicated data Flash memory

- > 12KB SRAM MEMORY WITH PARITY

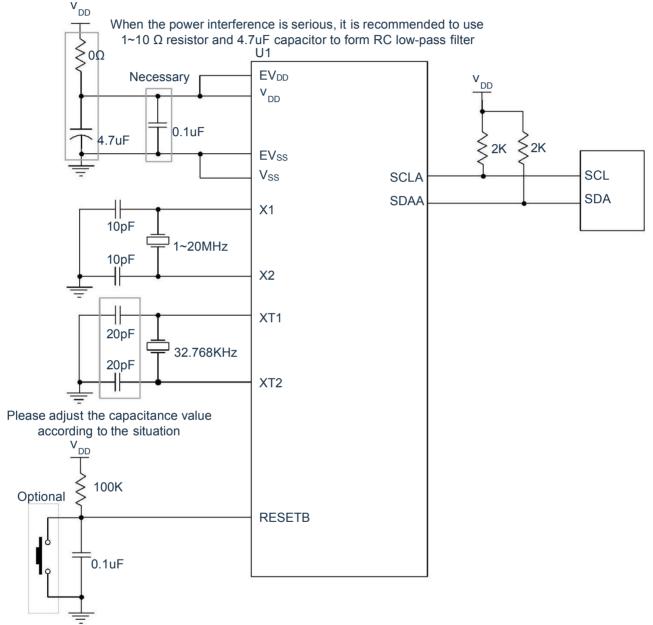

### • Power and reset management:

- Built-in power-on reset (POR) circuit

- Built-in voltage detection (LVD) circuit (threshold voltage settable).

### • Clock Management:

- Built-in high-speed vibrator, accuracy (±1%). 1MHz~48MHz system clock is available. 1MHz~64MHz peripheral module operation clock is available

- > Built-in 15KHz low-speed oscillator

- Support 1MHz~20MHz external crystal oscillator

- Supports 32.768KHz external crystal oscillator

### • Multiplier/ divider module:

- Multiplier: Supports single-cycle 32 bitmultiplication operations

- Divider: Supports 32bit signed integer division operations, only 4 or 8 CPU clock cycles to complete the operation

### • Enhanced DMA Controller:

- > The interrupt triggers the start.

- Selectable transfer modes (normal transfer mode, repeated transfer mode, block transfer mode and chain transfer mode)

#### Input/ output ports:

- > I/O ports: 29~59

- It can switch between N-channel open drain, TTL input buffering, and internal pull-up

- Built-in keys interrupt the checkout function

- Control circuit with built-in clock output/ buzzer output

### • Serial two-wire debugger (SWD).

### • Abundant timers:

- 16-bit timer: 9 channels with general-purpose PWM and motor-specific PWM functions

- 15-bit interval timer: 1

- Real-time clock (RTC): 1 (with perpetual calendar, alarm clock function, and supports a wide range of clock correction).

- Watchdog timer (WWDT): 1pcs

- SysTick timer

### Rich and flexible interfaces:

- Two serial communication units: serial communication unit 0 can be freely configured as 2-channel standard UART or 4-channel 3wire SPI or 4-channel simple I<sup>2</sup>C; Serial communication unit 1 can be freely configured as 1-channel standard UART, 2-channel 3wire SPI or 2-channel simple I<sup>2</sup>C; (UART of unit 0 supports LIN Bus communication, SPI00 channel supports 4-wire SPI communication)

- Standard I<sup>2</sup>C: 1 channel

- IrDA: 1 channel

- CAN: 1 channel

### Security features:

- Complies with IEC/ UL 60730 standards

- An abnormal storage space access error is reported

- Supports RAM parity

- Support hardware CRC verification

- Support important SFR protection to prevent misoperation

- > 128-bit unique ID number

- Grade 2 protection of F lash in debug mode (level 1: can only be erased in all areas of flash, cannot read and write; Level 2: The emulator connection is invalid and cannot be operated on flash).

The transmission source/ destination realm is selectable from the full address space range

### • Linkage controller:

- It can link event signals together to realize the linkage of peripheral functions

- There are 22 types of event input and 10 types of event triggering

### • Rich analog peripheral:

- 12-bit precision ADC converter with 1.06msps conversion rate, 16 external analog channels with temperature sensor support for single-channel conversion mode and multi-channel sweep conversion mode. Conversion range: 0 to positive reference voltage

- 8-bit precision D/ A converter, 1 or 2 channel analog output, real-time output function, output voltage range 0~V<sub>DD</sub>

- Comparator (CMP) with built-in twochannel comparator with selectable input source and selectable reference voltage external or internal reference

- Programmable gain amplifier (PGA) with built-in two-channel PGA programmable 4/ 8/ 10/ 12/ 14/ 16/ 32x gain with an external GND pin (available as differential mode).

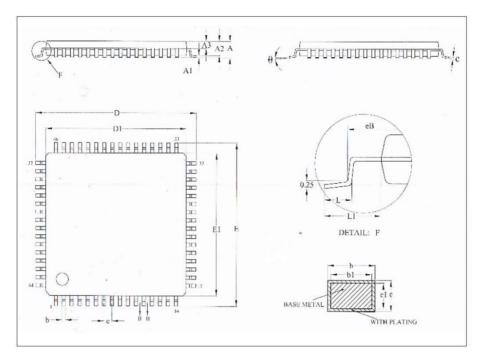

### • Package:

Support 24Pin~64Pin in a variety of package forms

# **1** Overview

# **1.1 Brief Introduction**

BAT32A237 series conforms to AEC-Q100 Grade1 automotive product standard, -40~125°C working environment temperature, supports 24~64Pin in a variety of QFN, LQFP packages. This product uses the high-performance ARM Cortex-M0®+ 32bit RISC core, which can operate at up to 48 MHz. High-speed embedded flash memory (the maximum SRAM is 12KB, and the maximum program/ data flash memory is 128KB). This product integrates I<sup>2</sup>C, SPI, UART, LIN, CAN bus and other standard interfaces, integrated 12bit A/ D converter, temperature sensor, 8bit D/ A converter, comparator, programmable gain amplifier. The 12bit A/ D converter can be used to acquire external sensor signals to reduce system design cost. The 8bit D/ A converter can be used for audio playback or power control. An integrated temperature sensor enables real-time monitoring of the external ambient temperature. An integrated comparator can be used in applications such as motor control feedback or battery monitoring. Integrate a variety of advanced timer modules, load 1-channel SysTick timer, 17-channel 16bit timer, 1-channel 15bit interval timer, watchdog timer and real-time clock and other functions, It can also support applications such as general-purpose PWM and motor-specific PWM.

The BAT32A237 also has excellent low-power performance, supporting both sleep and deep sleep modes for design flexibility. It consumes 120uA/ MHz@48MHz and consumes only 0.7uA in deep sleep mode. At the same time, due to the integrated event linkage controller, direct connection between hardware modules can be realized without CPU intervention, which is faster than using interrupts.

The BAT32A237 microcontroller family's excellent reliability, rich integrated peripheral functions, and excellent low-power performance make it suitable for a wide range of automotive product development.

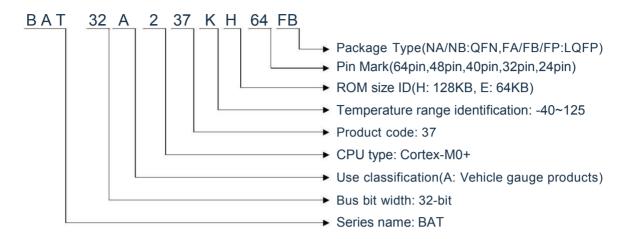

# 1.2 Product Model List

### Product List for BAT32A237:

| Number of pins | package                                             | Product model   |

|----------------|-----------------------------------------------------|-----------------|

| 24pins         | 24-pin plastic package LQFP<br>(4x4mm, 0.5mm pitch) | BAT32A237KE24NA |

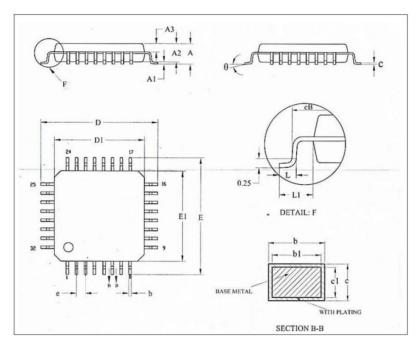

| 32 pins        | 32-pin plastic package LQFP<br>(7x7mm, 0.8mm pitch) | BAT32A237KH32FP |

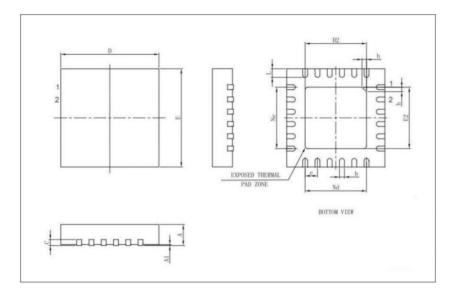

| 40 pins        | 40-pin plastic package QFN<br>(5x5mm, 0.4mm pitch)  | BAT32A237KH40NB |

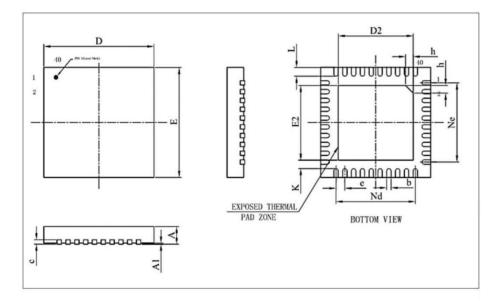

| 48 pins        | 48-pin plastic package LQFP<br>(7x7mm, 0.5mm pitch) | BAT32A237KH48FA |

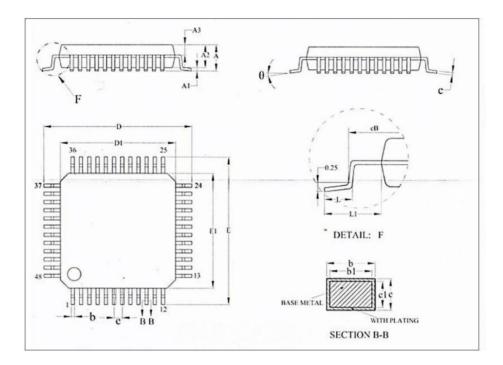

| 64 pins        | 64-pin plastic package LQFP<br>(7x7mm, 0.4mm pitch) | BAT32A237KH64FB |

#### FLASH, SRAM CAPACITY:

|  | Flash<br>memory | Specific data | CDAM | BAT32A237       |               |               |  |  |  |

|--|-----------------|---------------|------|-----------------|---------------|---------------|--|--|--|

|  |                 | Flash memory  | SRAM | 24 pins         | 32 pins       | 40 pins       |  |  |  |

|  | 64/128KB        | 1.5KB         | 12KB | BAT32A237KE24NA | BAT32A237KH32 | BAT32A237KH40 |  |  |  |

| F | Flash       | Specific data | CDAM | BAT32A237     |               |  |  |  |

|---|-------------|---------------|------|---------------|---------------|--|--|--|

| m | emory       | Flash memory  | SRAM | 48 pins       | 64 pins       |  |  |  |

| 1 | 128KB 1.5KB |               | 12KB | BAT32A237KH48 | BAT32A237KH64 |  |  |  |

#### Product Selection Table for BAT32A237:

| Part No.            | kernel | Clock speed (MHz) | Minimum operating voltage (V). | Maximum operating voltage (V). | Code Flash (KB) | SRAM (KB) | Data Flash (KB) | D MA | GPIO | 12bit ADC | 8bit DAC | Comparator CMP | Amplifier PGA | General-purpose timer (16bit). | Real-time clock (RTC). | Watchdog timer (WDT). | Asynchronous serial bus (UART). | Synchronous serial bus (SPI). | IC bus | IrDA bus | LIN bus | CAN bus | Hardware multiplier | Hardware divider | Package    |

|---------------------|--------|-------------------|--------------------------------|--------------------------------|-----------------|-----------|-----------------|------|------|-----------|----------|----------------|---------------|--------------------------------|------------------------|-----------------------|---------------------------------|-------------------------------|--------|----------|---------|---------|---------------------|------------------|------------|

| BAT32A237<br>KE24NA | M0+    | 48                | 2.0                            | 5.5                            | 64              | 12        | 1.5             | 35   | 21   | 8+3       | 1        | 2              | 1             | 9                              | 1                      | 1                     | 3                               | 3                             | 1+3    | 1        | 1       | 1       | Y                   | Y                | QFN<br>24  |

| BAT32A237<br>KH32FP | M0+    | 48                | 2.0                            | 5.5                            | 128             | 12        | 1.5             | 35   | 29   | 10+<br>3  | 2        | 2              | 1             | 9                              | 1                      | 1                     | 3                               | 3                             | 1+3    | 1        | 1       | 1       | Y                   | Y                | LQFP<br>32 |

| BAT32A237<br>KH40NB | M0+    | 48                | 2.0                            | 5.5                            | 128             | 12        | 1.5             | 36   | 37   | 12+<br>4  | 2        | 2              | 2             | 9                              | 1                      | 1                     | 3                               | 4                             | 1+4    | 1        | 1       | 1       | Y                   | Y                | QFN<br>40  |

| BAT32A237<br>KH48FA | M0+    | 48                | 2.0                            | 5.5                            | 128             | 12        | 1.5             | 36   | 45   | 15+<br>4  | 2        | 2              | 2             | 9                              | 1                      | 1                     | 3                               | 5                             | 1+5    | 1        | 1       | 1       | Y                   | Y                | LQFP<br>48 |

| BAT32A237<br>KH64FB | M0+    | 48                | 2.0                            | 5.5                            | 128             | 12        | 1.5             | 37   | 59   | 16+<br>4  | 2        | 2              | 2             | 9                              | 1                      | 1                     | 3                               | 6                             | 1+6    | 1        | 1       | 1       | Y                   | Y                | LQFP<br>64 |

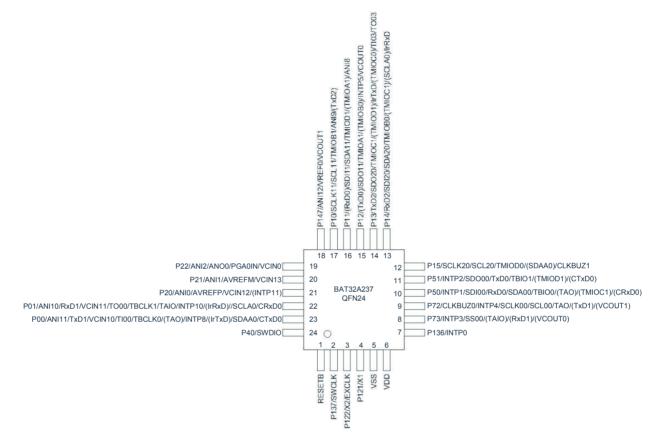

# 1.3 Top View

# 1.3.1 BAT32A237KE24NA

• 24-pin plastic QFN(4x4mm、 0.5mm pitch)

Note: The functions in () of the above Figure can be assigned by setting the peripheral I/ O redirection registers.

# 1.3.2 BAT32A237KH32FP

• 32-pin plastic LQFP (7x7mm, 0.8mm pitch).

Note: The functions in () of the above Figure can be assigned by setting the peripheral I/ O redirection registers.

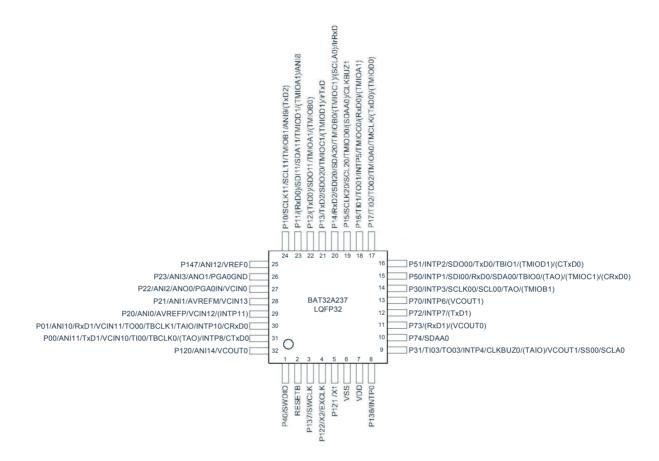

# 1.3.3 BAT32A237KH40NB

• 40-pin plastic QFN (5x5mm, 0.4mm pitch).

Note: The functions in () of the above Figure can be assigned by setting the peripheral I/ O redirection registers.

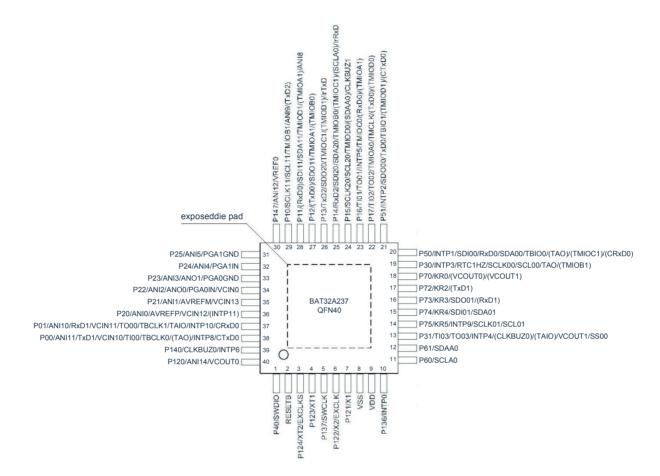

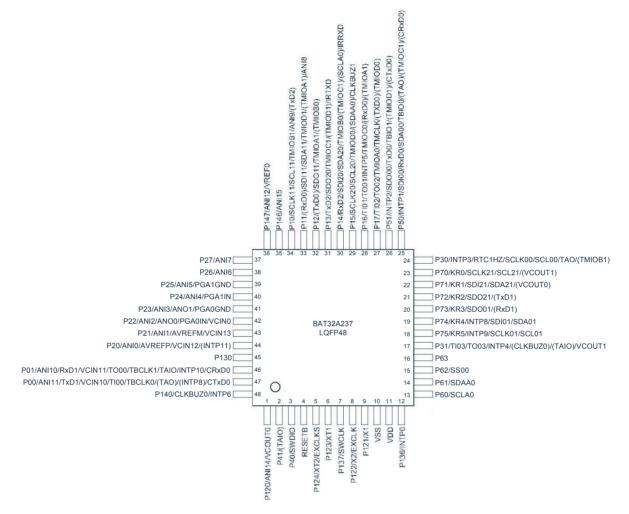

# 1.3.4 BAT32A237KH48FA

• 48-pin plastic LQFP (7x7mm, 0.5mm pitch).

Note: The functions in () of the above Figure can be assigned by setting the peripheral I/ O redirection register.

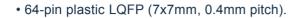

# 1.3.5 BAT32A237KH64FB

#### Note:

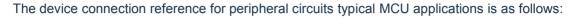

- 1. The  $EV_{SS}$  pin and  $V_{SS}$  pin must be the same potential.

- 2. The voltage at the  $V_{DD}$  pin must be equal to the voltage at the  $EV_{DD}$  pin.

- In the case where it is necessary to reduce the noise generated from the MCU in the application field, it is recommended to take noise countermeasures such as providing power to V<sub>DD</sub> and EV<sub>DD</sub> separately and grounding V<sub>SS</sub> and EV<sub>SS</sub> separately.

- 4. The functions in () of the above Figure can be assigned by setting the peripheral I/ O redirection registers.

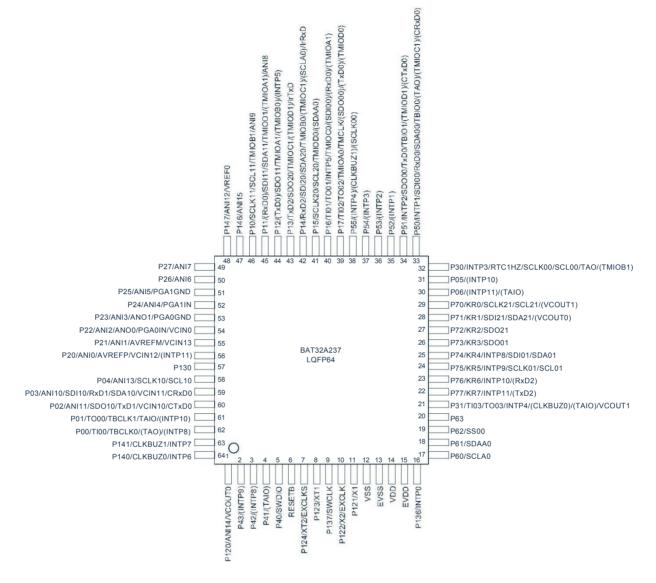

# 2 Product Structure Diagram

Note: The figure above is a block diagram of a 64-pin product, and some functions of products below 64pin are not supported.

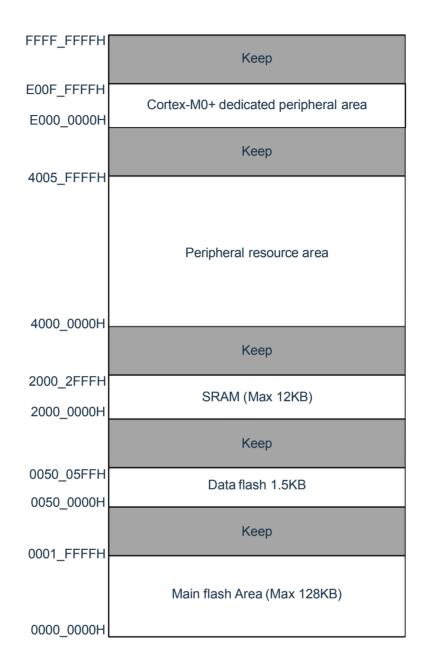

# 3 Memory Map

# **4** Pin Function

# 4.1 Port Functionality

The relationship between the power supply and the pins is shown below

64-pin product:

| Power/ Ground                       | The corresponding pin                                    |

|-------------------------------------|----------------------------------------------------------|

| EV <sub>DD</sub> / EV <sub>SS</sub> | Port pins other than P20~P27, P121~P124, P137 and RESETB |

| V <sub>DD</sub> / V <sub>SS</sub>   | • P20~P27, P121~P124, P137 and RESETB                    |

Products other than 64pins use a single power supply, and all pins are powered by  $V_{\text{DD}}$ .

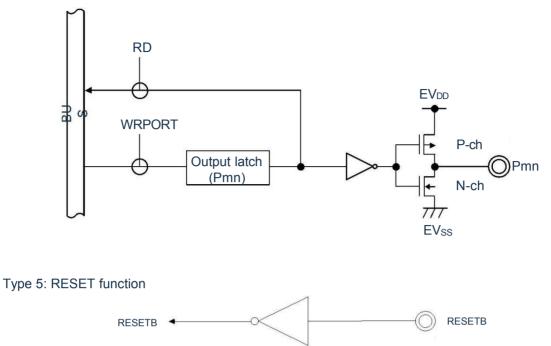

All ports of this product are divided into 5 types according to type, which are type1~type5, and the corresponding situation is as follows:

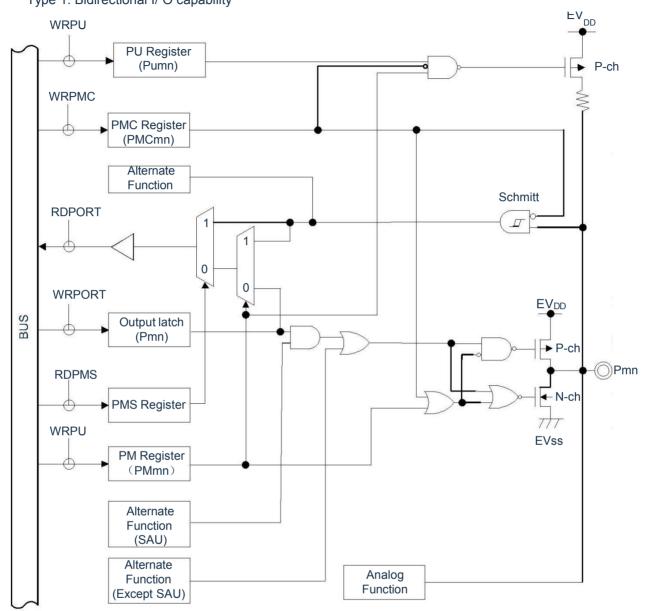

Type 1: Bidirectional I/ O capability

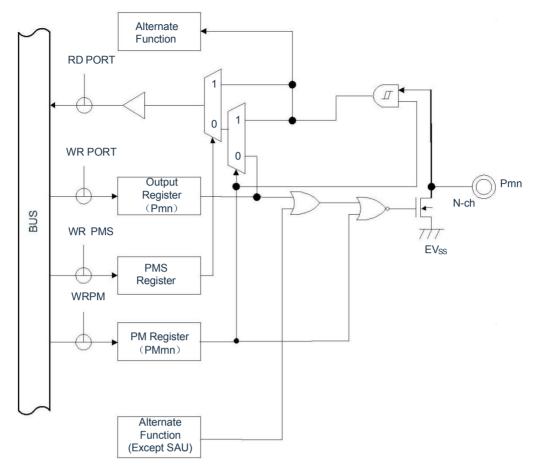

Type 2: NOD function, corresponding to pins P60-P63

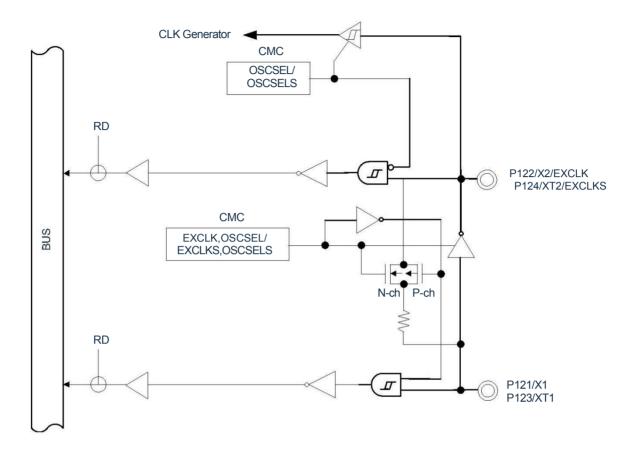

Type 3: Only input functions, such as clocks, correspond to pins P121-P124

Type 4: Only output function, corresponding to pin P130

Type 5: RESET function, corresponding to pin RESETB

The leadframe diagram of each type is detailed in 4.3 Port Types

# 4.1.1 24pin Product Pin Function Description

| Function name | Port<br>type | Input/<br>Output                     | After the reset is released | Multplexing features                                                    | Function                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                            |  |  |

|---------------|--------------|--------------------------------------|-----------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P00           |              |                                      |                             | ANI11/TxD1/VCIN10/TI00/TBCLK0/<br>(TAO) / (INTP8)<br>/IrTxD/SDAA0/CTxD0 | Port 0<br>3-bit input/ output ports that can be<br>specified as inputs or outputs in bits. The                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P01           |              | Input/<br>Output                     | Input port                  | ANI10/RxD1/VCIN11/TO00/TBCLK1/<br>TAIO/ (INTP10)<br>/IrRxD/SCLA0/CRxD0  | input port can be set by software using<br>internal pull-up resistors.<br>The input of P01 can be set to TTL input<br>buffer.                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P06           |              |                                      |                             | SCLK11/SCL11/TMIOB1/ANI9/(TxD2)                                         | The output of P00 can be set to an N-<br>channel open-drain output (V <sub>DD</sub> withstand<br>voltage).                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P10           |              |                                      | Analog                      | (RxD0) /SDI11/SDA11/TMIOD1/<br>(TMIOA1) /ANI8                           | Port 1<br>3-bit input/ output ports that can be                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P11           |              |                                      | function                    | (TxD0) /SDO11/TMIOA1/<br>(TMIOB0) / (INTP5) /VCOUT0                     | specified as inputs or outputs in bits. The input port can be set by software using                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P12           |              | Input/<br>Output                     |                             | Input port                                                              | TxD2/SDO20/TMIOC1/(TMIOD1)<br>/IrTxD/TI03/TO03                                                                                                                                                                                                                                                                                                      | internal pull-up resistors.<br>The inputs of P10 can be set to TTL Input buffering.<br>The outputs of P10 and P11 can be set to N-channel open-drain output $(V_{DD}$ withstand voltage).<br>P10 and P11 can be set as analog inputs.                                                                                                                      |  |  |

| P20           |              |                                      |                             | RxD2/SDI20/SDA20/ TMIOB0/<br>(TMIOC1) / (SCLA0) /IrRxD                  | Port 2                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P21           | 8            | Input/<br>Output                     | Analog<br>function          | SCLK20/SCL20/TMIOD0/ (SDAA0)                                            | 3-bit input/ output ports that can be specified as inputs or outputs in bits. Can                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P22           | Type 1       | - adpart                             |                             | /CLKBUZ1<br>ANI0/AVREFP/VCIN12/ (INTP11)                                | be set as an analog input.                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P30           |              | Input/<br>Output<br>Input/<br>Output | Input port                  | ANI1/AVREFM/VCIN13                                                      | Port 3<br>1-bit input/ output ports that can be<br>specified as inputs or outputs in bits. The<br>input port can be set by software using<br>internal pull-up resistors.<br>The input of P30 can be set to TTL input<br>buffering. The output of P30 can be set to<br>N-channel open-drain output (V <sub>DD</sub><br>withstand voltage).<br>Port 4 |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P40           |              |                                      | Input port                  | ANI2/ANO0/PGA0IN/VCIN0                                                  | 1-bit input/ output port, can be specified as<br>input or output. The input port can be set<br>by software using internal pull-up<br>resistors.                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P50           |              |                                      |                             | SWDIO                                                                   | Port 5                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P51           |              | Input/<br>Output                     |                             | Input port                                                              | INTP1/SDI00/RxD0/SDA00/TBIO0/<br>(TAO) / (TMIOC1) / (CRxD0)                                                                                                                                                                                                                                                                                         | 2-bit input/ output ports that can be<br>specified as inputs or outputs in bits. The<br>input port can be set by software using<br>internal pull-up resistors.<br>The input of the P50 can be set to TTL<br>input buffer.<br>The outputs of the P50 and P51 can be set<br>to an open-drain output of the N-channel<br>(V <sub>DD</sub> withstand voltage). |  |  |

| P71           |              | Input/                               | Input port                  | INTP2/SDO00/TxD0/TBIO1/                                                 | Port 7                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                            |  |  |

|               |              | Output                               |                             | (TMIOD1) / (CTxD0)                                                      | 3-bit input/ output ports that can be                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| P72          |        |                  |                    | CLKBUZ0/INTP4/SCLK00/SCL00/T<br>AO/(TxD1)/(VCOUT1) | specified as inputs or outputs in bits. The<br>input port can be set by software using<br>– internal pull-up resistors.                                                                               |  |  |

|--------------|--------|------------------|--------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P73          |        |                  |                    | INTP3/SS00/(TAIO)/(RxD1)/<br>(VCOUT0)              | $(V_{DD} \text{ withstand voltage}).$                                                                                                                                                                 |  |  |

| P121<br>P122 | Туре 3 | Input            | Input port         | X1<br>X2/EXCLK                                     | Port 12<br>2-bit input/ output port                                                                                                                                                                   |  |  |

| P136         |        | Input/           | Input port         | INTP0                                              | _ Port 13                                                                                                                                                                                             |  |  |

| P137         |        | Output           | Input port         | SWCLK                                              | 2-bit input/ output port                                                                                                                                                                              |  |  |

| P147         | Type 1 | Input/<br>Output | Analog<br>function | ANI12/VREF0/VCOUT1                                 | Port 14<br>1-bit input/ output port, can be specified as<br>input or output. The input port can be set<br>by software using internal pull-up<br>resistors.<br>The P147 can be set as an analog input. |  |  |

| RESETB       | Type 5 | Input            | _                  | _                                                  | An input dedicated pin for external reset,<br>which must be connected directly or<br>through a resistor to $V_{DD}$ when external<br>reset is not in use.                                             |  |  |

# 4.1.2 32pin product pin function description

(1/2)

| Function<br>name | Port<br>type | Input/<br>output | After the reset is released | Multplexing features                                     | Function                                                                                                                                                                                                                                                                                  |

|------------------|--------------|------------------|-----------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00              |              |                  |                             | ANI11/TxD1/VCIN10/TI00/TBCLK0/<br>(TAO)<br>/INTP8/CTxD0  | Port 0<br>2-bit input/ output ports that can be specified<br>as inputs or outputs in bits. The input port                                                                                                                                                                                 |

| P01              |              |                  | Analog<br>function          | ANI10/RxD1/VCIN11/TO00/<br>TBCLK1<br>/TAIO/INTP10/CRxD0  | can be set by software using internal pull-<br>up resistors.<br>The input of P01 can be set to TTL input<br>buffer.<br>The output of P00 can be set to an N-<br>channel open-drain output (V <sub>DD</sub> withstand<br>voltage).<br>P00 and P01 can be set as analog inputs.             |

| P10              |              |                  | Analog                      | SCLK11/SCL11/TMIOB1/ANI9/ (<br>TxD2)                     |                                                                                                                                                                                                                                                                                           |

| P11              |              |                  | function                    | (RxD0) /SDI11/SDA11/TMIOD1/ (<br>TMIOA1) /ANI8           |                                                                                                                                                                                                                                                                                           |

| P12              |              |                  |                             | (TxD0) /SDO11/TMIOA1/ (<br>TMIOB0)                       | Port 1<br>8-bit input/ output ports that can be specified<br>as inputs or outputs in bits. The input port                                                                                                                                                                                 |

| P13              |              |                  |                             | TxD2/SDO20/TMIOC1/ (TMIOD1)<br>/IrTxD                    | can be set by software using internal pull-                                                                                                                                                                                                                                               |

| P14              |              | Input/<br>Output |                             | RxD2/SDI20/SDA20/ TMIOB0/(<br>TMIOC1)<br>/(SCLA0)/IrRxD  | up resistors.<br>The inputs of P10 and P14~P17 can be set<br>to TTL                                                                                                                                                                                                                       |

| P15              | Turne 1      |                  | Input port                  | SCLK20/SCL20/TMIOD0/(<br>SDAA0)/CLKBUZ1                  | Input buffering.<br>The outputs of P10, P11, P13~ P15 and P17                                                                                                                                                                                                                             |

| P16              | Type 1       |                  |                             | TI01/TO01/INTP5/TMIOC0/(RxD0<br>)<br>/(TMIOA1)           | can be set to N-channel open-drain output $(V_{DD}$ withstand voltage).<br>P10 and P11 can be set as analog inputs.                                                                                                                                                                       |

| P17              |              |                  |                             | TI02/TO02/TMIOA0/TMCLK/ (<br>TxD0)<br>/ (TMIOD0)         |                                                                                                                                                                                                                                                                                           |

| P20              |              |                  |                             | ANI0/AVREFP/VCIN12/ (INTP11)                             | Port 2                                                                                                                                                                                                                                                                                    |

| P21              |              |                  | Analog                      | ANI1/AVREFM/VCIN13                                       | 4-bit input/ output ports that can be                                                                                                                                                                                                                                                     |

| P22              |              | Output           | function                    | ANI2/ANO0/PGA0IN/VCIN0                                   | specified as inputs or outputs in bits.                                                                                                                                                                                                                                                   |

| P23              |              |                  |                             | ANI3/ANO1/PGA0GND                                        | Can be set as an analog input.                                                                                                                                                                                                                                                            |

| P30              |              |                  |                             | INTP3/SCLK00/SCL00/TAO/<br>(TMIOB1)                      | Port 3<br>2-bit input/ output ports that can be specified                                                                                                                                                                                                                                 |

| P31              |              | Input/<br>Output | Input port                  | TI03/TO03/INTP4/CLKBUZ0/(TAIO<br>)/VCOUT1<br>/SS00/SCLA0 | as inputs or outputs in bits. The input port<br>can be set by software using internal pull-<br>up resistors.<br>The inputs of P30 and P31 can be set to TTL<br>input buffering. The outputs of P30 and P31<br>can be set to N-channel open-drain output<br>( $V_{DD}$ withstand voltage). |

| P40              |              | Input/<br>Output | Input port                  | SWDIO                                                    | Port 4<br>1-bit input/ output port, can be specified as<br>input or output. The input port can be set by<br>software using internal pull-up resistors.                                                                                                                                    |

(2/2)

|               |                            |                  |                             | *                                              |                                                                                                                                                                                                        |

|---------------|----------------------------|------------------|-----------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function name | Port<br>type               | Input/<br>Output | After the reset is released | Multplexing features                           | Function                                                                                                                                                                                               |

|               |                            |                  |                             | INTP1/SDI00/RxD0/SDA00                         | Port 5                                                                                                                                                                                                 |

| P50           |                            |                  |                             | /TBIO0/ (TAO) / (TMIOC1)<br>/ (CRxD0)          | 2-bit input/ output ports that can be specified<br>as inputs or outputs in bits. The input port can<br>be set by software using internal pull-up                                                       |

| P51           | Type 1                     | Input/<br>Output | Input port                  | INTP2/SDO00/TxD0/TBIO1<br>/ (TMIOD1) / (CTxD0) | resistors.<br>The input of the P50 can be set to TTL input<br>buffer.<br>The outputs of the P50 and P51 can be set to<br>an open-drain output of the N-channel (V <sub>DD</sub><br>withstand voltage). |

| P70           |                            |                  |                             | INTP6/ (VCOUT1)                                | Port 7                                                                                                                                                                                                 |

| P72           |                            | Input/           |                             | INTP7/ (TxD1)                                  | 4-bit input/output port, which can be specified<br>as input or output in bits. The input port can                                                                                                      |

| P73           |                            |                  |                             | (RxD1) / (VCOUT0)                              | use internal pull-up resistance through                                                                                                                                                                |

| P74           | Type 1                     | Output           | Input port                  | SDAA0                                          | software settings.<br>The input of the P74 can be set to TTL input<br>buffer and the output can be set to an N-<br>channel open-drain output (V <sub>DD</sub> withstand<br>voltage).                   |

| P120          |                            | Input/<br>Output | Analog<br>function          | ANI14/VCOUT0                                   | Port 12<br>1-bit input/ output port and 2-bit input                                                                                                                                                    |

| P121          |                            |                  |                             | X1                                             | dedicated port                                                                                                                                                                                         |

| P122          | Туре 3                     | Input            | It Input port               | X2/EXCLK                                       | Only the P120 has an output function. Only the input port of the P120 can be set by software to use internal pull-up resistors. The P120 can be set as an analog input.                                |

| P136          |                            | Input/           | Input port                  | INTP0                                          | Port 13                                                                                                                                                                                                |

| P137          |                            | Output           | Input port                  | SWCLK                                          | 2-bit input/ output port                                                                                                                                                                               |

| P147          | Type 1<br>Input/<br>Output |                  | Analog<br>function          | ANI12/VREF0                                    | Port 14<br>1-bit input/ output port, can be specified as<br>input or output. The input port can be set by<br>software using internal pull-up resistors.<br>The P147 can be set as an analog input.     |

| RESETB        | Type 5                     | Input            | _                           | _                                              | An input dedicated pin for external reset, which must be connected directly or through a resistor to $V_{DD}$ when external reset is not in use.                                                       |

Note:

- 1. Each pin can be set to digital or analog (can be set in bits) via port mode control register x (PMCx).

- 2. For a description of the multiplexing function, see "4.2 Port Multiplexing Function".

- 3. The functions in the table above () can be assigned by setting the peripheral I/ O redirection registers.

# 4.1.3 40pin Product Pin Function Description

(1/2)

| Feature<br>name | Port<br>type | Input/<br>output | After the reset is released | Multplexing features                                                        | Function                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |  |

|-----------------|--------------|------------------|-----------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| P00             |              |                  |                             | ANI11/TxD1/VCIN10/TI00/TBCLK0                                               | Port 0                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |  |

| P01             |              | Input/<br>Output | Analog<br>function          | / (TAO) /INTP8/CTxD0<br>ANI10/RxD1/VCIN11/TO00/TBCLK1<br>/TAIO/INTP10/CRxD0 | 2-bit input/ output ports that can be<br>specified as inputs or outputs in bits. The<br>input port can be set by software using<br>internal pull-up resistors.<br>The input of P01 can be set to TTL input<br>buffer. The output of the P00 can be set<br>to an N-channel open-drain output (V <sub>DD</sub><br>withstand voltage).<br>P00 and P01 can be set as analog<br>inputs. |                                                                                                                            |  |

| P10             |              |                  | Analog                      | SCLK11/SCL11/TMIOB1/ANI9/ (TxD2)                                            |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |  |

| P11             |              |                  | function                    | (RxD0) /SDI11/SDA11/TMIOD1/ (TMIOA1)<br>/ANI8                               | Port 1<br>8-bit input/ output ports that can be                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |  |

| P12             |              |                  |                             | (TxD0) /SDO11/TMIOA1/ (TMIOB0)                                              | specified as inputs or outputs in bits. The                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |  |

| P13             |              |                  |                             | TxD2/SDO20/TMIOC1/ (TMIOD1) /IrTxD                                          | input port can be set by software using<br>internal pull-up resistors.                                                                                                                                                                                                                                                                                                             |                                                                                                                            |  |

| P14             |              | Input/<br>Output |                             | RxD2/SDI20/SDA20/ TMIOB0/(TMIOC1)/(<br>SCLA0)/IrRxD                         | The inputs of P10 and P14~P17 can be set to TTL input buffer.                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |  |

| P15             |              |                  |                             | Input port                                                                  | SCLK20/SCL20/TMIOD0/ (SDAA0)<br>/CLKBUZ1                                                                                                                                                                                                                                                                                                                                           | The outputs of P10, P11, P13~ P15 and                                                                                      |  |

| P16             |              |                  |                             |                                                                             | TI01/TO01/INTP5/TMIOC0/ (RxD0) / (<br>TMIOA1)                                                                                                                                                                                                                                                                                                                                      | P17 can be set to N-channel open-drain<br>outputs (V <sub>DD</sub> withstand voltage).<br>P10 and P11 can be set as analog |  |

| P17             | Type 1       |                  |                             | TI02/TO02/TMIOA0/TMCLK/ (TxD0) / (<br>TMIOD0)                               | inputs.                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |  |

| P20             |              |                  |                             | ANI0/AVREFP/VCIN12/ (INTP11)                                                |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |  |

| P21             |              |                  |                             | ANI1/AVREFM/VCIN13                                                          | Port 2                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |  |

| P22             |              | Input/           | Analog                      | ANI2/ANO0/PGA0IN/VCIN0                                                      | 6-bit input/ output ports that can be                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |  |

| P23             |              | Output           | function                    | ANI3/ANO1/PGA0GND                                                           | specified as inputs or outputs in bits. Can                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |  |

| P24             |              |                  |                             | ANI4/PGA1IN                                                                 | be set as an analog input.                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |  |

| P25             |              |                  |                             | ANI5/PGA1GND                                                                |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |  |

| P30             |              |                  |                             | INTP3/RTC1HZ/SCLK00/SCL00/TAO/ (<br>TMIOB1)                                 | Port 3<br>2-bit input/ output ports that can be                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |  |

| P31             |              | Input/<br>Output |                             | TI03/TO03/INTP4/CLKBUZ0/ (TAIO)<br>/VCOUT1/SS00                             | specified as inputs or outputs in bits. The input port can be set by software using internal pull-up resistors.<br>The input of the P30 can be set to TTL input buffering. The output of the P30 can be set to an N-channel open-drain output (V <sub>DD</sub> withstand voltage).                                                                                                 |                                                                                                                            |  |

| P40             |              | Input/<br>Output | Input port                  | SWDIO                                                                       | Port 4<br>1-bit input/ output port, can be specified<br>as input or output. The input port can be<br>set by software using internal pull-up<br>resistors.                                                                                                                                                                                                                          |                                                                                                                            |  |

(2/2)

| Function name | Port<br>type            | Input/<br>output | After the reset is released | Multplexing features                        | function                                                                                                                                                                                                                                            |  |  |  |

|---------------|-------------------------|------------------|-----------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P50           |                         |                  |                             | INTP1/SDI00/RxD0/SDA00/TBIO0/ (TAO) /       | Port 5                                                                                                                                                                                                                                              |  |  |  |

| F 50          |                         |                  |                             | (TMIOC1) / (CRxD0)                          | 2-bit input/ output ports that can be specified as inputs or outputs in bits. The                                                                                                                                                                   |  |  |  |

| P51           | Type 1 Input/<br>Output |                  | Input port                  | INTP2/SDO00/TxD0/TBIO1/(TMIOD1)/(<br>CTxD0) | input port can be set by software using<br>internal pull-up resistors.<br>The input of the P50 can be set to TTL<br>input buffer. The outputs of the P50 and<br>P51 can be set to an N-channel open-<br>drain output ( $V_{DD}$ withstand voltage). |  |  |  |

| P60           |                         |                  |                             | SCLA0                                       | Port 6                                                                                                                                                                                                                                              |  |  |  |

| P61           | Type 2                  | Input/<br>Output | Input port                  | SDAA0                                       | 2-bit input/ output ports that can be<br>specified as inputs or outputs in bits.<br>The output of P60~ P61 is an N-channel<br>open-drain output (6V withstand voltage).                                                                             |  |  |  |

| P70           |                         |                  |                             | KR0/ (VCOUT0) / (VCOUT1)                    | Port 7                                                                                                                                                                                                                                              |  |  |  |

| P72           |                         |                  |                             | KR2/ (TxD1)                                 | 5-bit input/ output ports that can be<br>specified as inputs or outputs in bits.                                                                                                                                                                    |  |  |  |

| P73           |                         | Input/           | Input port                  | KR3/SDO01/ (RxD1)                           | input port can be set by software using                                                                                                                                                                                                             |  |  |  |

| P74           | Type 1                  | Output           | πραιροτ                     | KR4/SDI01/SDA01                             | internal pull-up resistors.                                                                                                                                                                                                                         |  |  |  |

| P75           |                         |                  |                             | KR5/INTP9/SCLK01/SCL01                      | The P74 output can be set to an N-<br>channel open-drain output (V <sub>DD</sub><br>withstand voltage).                                                                                                                                             |  |  |  |

| P120          |                         | Input/<br>Output | Analog<br>function          | ANI14/VCOUT0                                | Port 12<br>1-bit input output port and 4-bit input                                                                                                                                                                                                  |  |  |  |

| P121          |                         |                  |                             | X1                                          | dedicated port                                                                                                                                                                                                                                      |  |  |  |

| P122          |                         |                  |                             | X2/EXCLK                                    | Only the P120 has an output function.<br>Only the input port of the P120 can be                                                                                                                                                                     |  |  |  |

| P123          | Type 3                  | Input            | Input port                  | XT1                                         | _ set by software to use internal pull-up                                                                                                                                                                                                           |  |  |  |

| P124          |                         |                  |                             | XT2/EXCLKS                                  | resistors. The P120 can be set as an analog input.                                                                                                                                                                                                  |  |  |  |

| P136          |                         | Input/           | Input port                  | INTP0                                       | Port 13                                                                                                                                                                                                                                             |  |  |  |

| P137          | Type 1                  | Output           |                             | SWCLK                                       | 2-bit input/ output port.                                                                                                                                                                                                                           |  |  |  |

| P140          |                         |                  | Input port                  | CLKBUZ0/INTP6                               | Port 14                                                                                                                                                                                                                                             |  |  |  |

| P147          |                         | Input/<br>Output | Analog<br>function          | ANI12/VREF0                                 | 2-bit input/ output ports that can be<br>specified as inputs or outputs in bits. The<br>input port can be set by software using<br>internal pull-up resistors.<br>The P147 can be set as an analog input.                                           |  |  |  |

| RESETB        | Туре 5                  | Input            | _                           |                                             | An input dedicated pin for external reset that must be connected to $V_{\text{DD}}$ directly or through a resistor when external reset is not in use.                                                                                               |  |  |  |

Note:

- Each pin can be set to digital or analog (can be set in bits) via port mode control register x (PMCx).

- 2. For a description of the multiplexing function, see "4.2 Port Multiplexing Function".

- 3. The functions in the table above () can be assigned by setting the peripheral I/ O redirection registers.

# 4.1.4 48pin Product Pin Function Description

(1/2)

| Feature<br>name | port<br>type | Input/<br>output | After the reset is released | Multplexing features                                                    | function                                                                                                                                                                                                                                                                                                                                                                       |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

|-----------------|--------------|------------------|-----------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------|--|--|--|---|------------|------------------------------------------|----------------------------------------------------------|

| P00             |              |                  |                             | ANI11/TxD1/VCIN10/TI00/TBCLK0/ (TAO)                                    | Port 0                                                                                                                                                                                                                                                                                                                                                                         |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

| P01             |              | Input/<br>Output | Analog<br>function          | / (INTP8) /CTxD0<br>ANI10/RxD1/VCIN11/TO00/TBCLK1<br>/TAIO/INTP10/CRxD0 | 2-bit input/ output ports that can be<br>specified as inputs or outputs in bits. The<br>input port can be set by software using<br>internal pull-up resistors.<br>The input of P01 can be set to TTL input<br>buffer. The output of the P00 can be set<br>to an N-channel open-drain output (V <sub>DD</sub><br>withstand voltage).<br>P00 and P01 can be set as analog inputs |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

| P10             |              |                  | Analog                      | SCLK11/SCL11/TMIOB1/ANI9/ (TxD2)                                        |                                                                                                                                                                                                                                                                                                                                                                                |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

| P11             |              |                  | Analog<br>function          | (RxD0) /SDI11/SDA11/TMIOD1/ (TMIOA1<br>) /ANI8                          | Port 1<br>8-bit input/ output ports that can be                                                                                                                                                                                                                                                                                                                                |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

| P12             |              |                  |                             | (TxD0) /SDO11/TMIOA1/ (TMIOB0)                                          | specified as inputs or outputs in bits. The input port can be set by software using                                                                                                                                                                                                                                                                                            |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

| P13             |              |                  |                             | TxD2/SDO20/TMIOC1/ (TMIOD1) /IrTxD                                      | internal pull-up resistors.                                                                                                                                                                                                                                                                                                                                                    |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

| P14             |              | Input/<br>Output |                             | RxD2/SDI20/SDA20/ TMIOB0/(TMIOC1)/<br>(SCLA0)/IrRxD                     | The inputs of P10 and P14~P17 can be set to TTL                                                                                                                                                                                                                                                                                                                                |                                               |                                                                               |  |  |  |   |            |                                          |                                                          |

| P15             |              |                  |                             |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                |                                               |                                                                               |  |  |  | · | Input port | SCLK20/SCL20/TMIOD0/ (SDAA0)<br>/CLKBUZ1 | Input buffering.<br>The outputs of P10, P11, P13~P15 and |