# **CMS79F11x User Manual**

8-bit CMOS microcontroller with enhanced flash memory

Rev. 1.30

Please be reminded about following CMS's policies on intellectual property

\* Cmsemicon Limited(denoted as 'our company' for later use) has already applied for relative patents and entitled legal rights. Any patents related to CMS's MCU or other producrts is not authorized to use. Any individual, organization or company which infringes our company's interlectual property rights will be forbidden and stopped by our company through any legal actions, and our company will claim the lost and required for compensation of any damage to the company.

$\star$  The name of Cmsemicon Limited and logo are both trademarks of our company.

\* Our company preserve the rights to further elaborate on the improvements about products function, reliability and design in this manual. However, our company is not responsible for any usage about this manual. The applications and their purposes in this manual are just for clarification, our company does not guarantee that these applications are feasible without further improvements and changes, and our company does not recommend any usage of the products in areas where people's safety is endangered during accident. Our company's products are not authorized to be used for life-saving or life support devices and systems.

### Manual

| 1. PF | RODUCT DESCRIPTION                         | 6     |

|-------|--------------------------------------------|-------|

| 1.1   | Features                                   |       |

| 1.2   | System structure                           |       |

| 1.3   | PIN CONFIGURATION                          |       |

| 1.3   | 3.1 CMS79F111                              |       |

| 1.3   | 3.2 CMS79F112                              | 8     |

| 1.3   | 3.3 CMS79F113                              | 8     |

| 1.3   | 3.4 CMS79F116                              |       |

| 1.4   | SYSTEM CONFIGURATION REGISTER              |       |

| 1.5   | ONLINE SERIAL PROGRAMMING                  |       |

| 2. CI | ENTRAL PROCESSING UNIT (CPU)               | 13    |

| 2.1   | Memory                                     |       |

| 2.1   | 1.1 Program Memory                         |       |

| 2.1   | 1.2 Data Memory                            |       |

| 2.2   | Addressing Mode                            |       |

| 2.2   | 2.1 Direct Addressing                      |       |

| 2.2   | 2.2 Immediate Addressing                   |       |

| 2.2   | 2.3 Indirect Addressing                    | 23    |

| 2.3   | Stack                                      |       |

| 2.4   | ACCUMULATOR (ACC)                          |       |

|       | 4.1 General                                |       |

|       | 4.2 ACC Applications                       |       |

| 2.5   | PROGRAM STATUS REGISTER (STATUS)           |       |

| 2.6   | Pre-scaler (OPTION_REG)                    |       |

| 2.7   | PROGRAM COUNTER (PC)                       |       |

| 2.8   |                                            |       |

|       | 8.1 WDT Period.                            |       |

|       | 8.2 Watchdog Timer Control Register WDTCON |       |

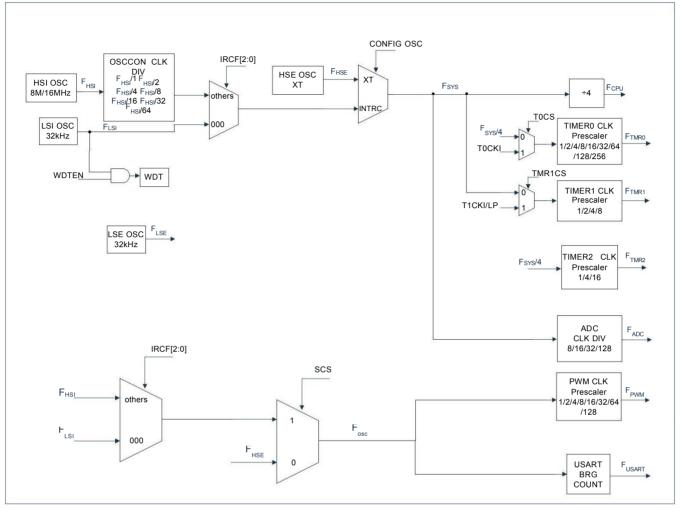

| 3. SY | YSTEM CLOCK                                |       |

| 3.1   | General                                    |       |

| 3.2   | System Oscillator                          |       |

| 3.2   | 2.1 Internal RC Oscillation                |       |

| 3.2   | 2.2 External XT Oscillation                |       |

| 3.3   | RESET TIME                                 |       |

| 3.4   | OSCILLATOR CONTROL REGISTER                |       |

| 3.5   | CLOCK BLOCK DIAGRAM                        |       |

| 4. RI | ESET                                       |       |

| 4.1   | Power on Reset                             |       |

| 4.2   | Power off Reset                            |       |

| 4.2   | 2.1 General                                |       |

| 4.2   | 2.2 Improvements for Power off Reset       |       |

| 4.3   | WATCHDOG RESET                             |       |

| 5. SI | LEEP MODE                                  |       |

| 5.1   | Enter Sleep Mode                           |       |

| 5.2   | Awaken from Sleep Mode                     |       |

| 5.3   | Interrupt Awakening                        |       |

| 5.4   | SLEEP MODE APPLICATION                     |       |

| 5.5   | SLEEP MODE AWAKEN TIME                     |       |

|       | 2 / 150                                    | V1.30 |

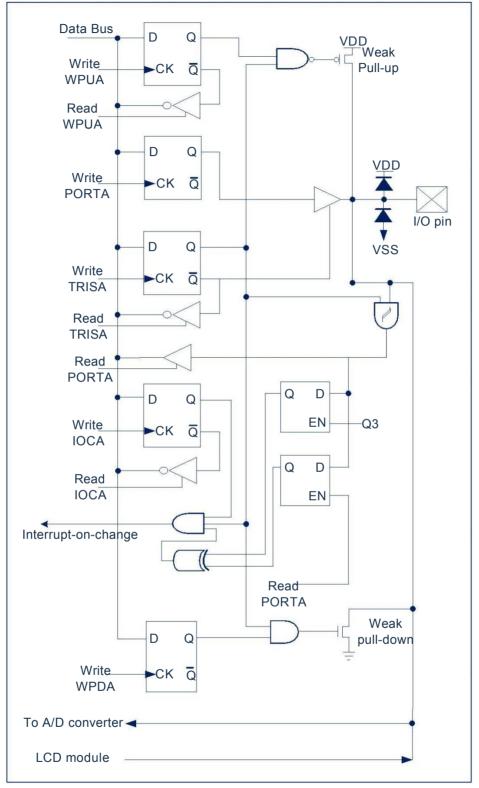

| 6. I       | /O P       | ORT                                                              | .42  |

|------------|------------|------------------------------------------------------------------|------|

| 6.1        | 1/         | O Port Structure                                                 | . 43 |

| 6.2        | F          | PORTA                                                            | 45   |

| 6          | 5.2.1      | PORTA Data and Direction Control                                 | 45   |

| 6          | 5.2.2      | PORTA Pull Up Resistance                                         | 46   |

| 6          | 5.2.3      | PORTA Pull Down Resistance                                       | 46   |

| 6          | 5.2.4      | PORTA Analog Control Selection                                   | 47   |

| 6          | 5.2.5      | PORTA Level Chage Interrupt                                      | 47   |

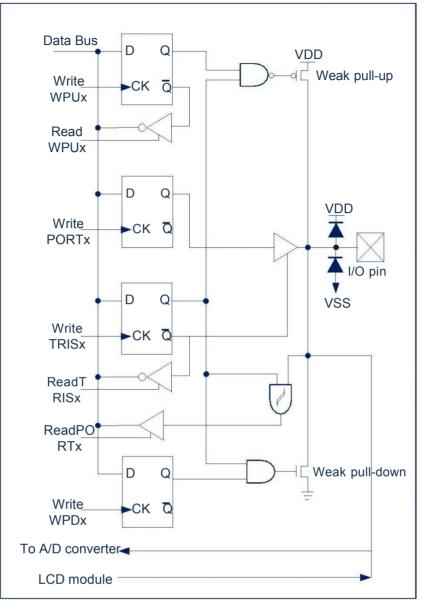

| 6.3        | F          | PORTB                                                            | 49   |

| 6          | 5.3.1      | PORTB Data and Direction                                         | 49   |

| 6          | 5.3.2      | PORTB Pull up Resistance                                         | 50   |

| 6          | 5.3.3      | PORTB Pull Down Resistance                                       | 50   |

| 6          | 5.3.4      | PORTB Analog Selection Control                                   | 51   |

| 6.4        | F          | PORTC                                                            | 52   |

| 6          | 5.4.1      | PORTC Data and Direction                                         | 52   |

| 6          | 5.4.2      | PORTC pull up resistance                                         | 53   |

| 6          | 5.4.3      | PORTC Pull Down Resistance.                                      | 53   |

| 6          | 5.4.4      | PORTC Analog Selection Control                                   | 54   |

| 6.5        | 1/         | O Usage                                                          |      |

| 6          | 6.5.1      | Write I/O port                                                   | .55  |

| 6          | 6.5.2      | Read I/O Port                                                    | 55   |

| 6.6        | F          | PRECAUTIONS FOR I/O PORT USAGE                                   | . 56 |

| <b>7</b> 1 |            |                                                                  | 57   |

| /. I       |            | RRUPT                                                            | .57  |

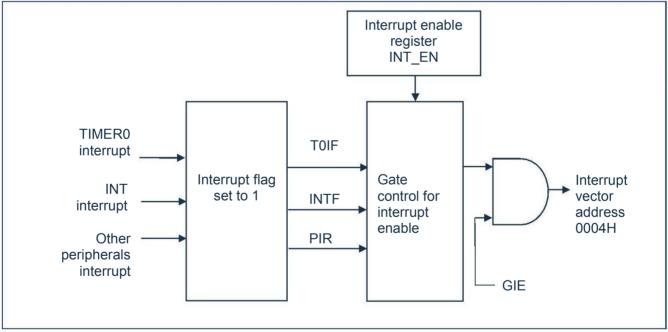

| 7.1        | I          | NTERRUPT GENERAL                                                 | . 57 |

| 7.2        | I          |                                                                  | . 58 |

| 7          | 7.2.1      | Interrupt Control Register                                       | 58   |

| 7          | 7.2.2      | Peripherals Interrupt Enable Register                            |      |

| 7          | 7.2.3      | Peripherals Interrupt Request Register                           |      |

| 7.3        |            | PROTECTION METHODS FOR INTERRUPT                                 |      |

| 7.4        | I          | NTERRUPT PRIORITY AND MULTI-INTERRUPT NESTING                    | . 61 |

| 8. 1       | ГІМЕ       | R0                                                               | 62   |

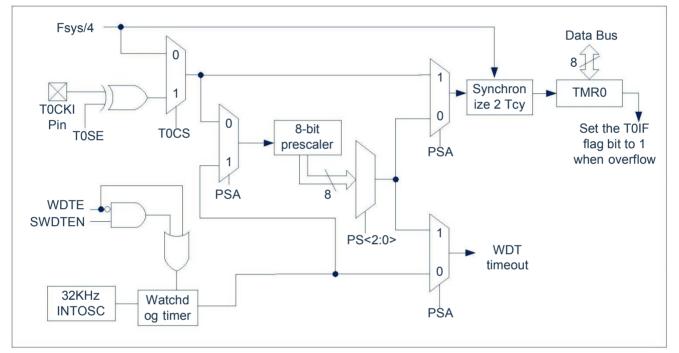

| 8.1        |            | IMER0 General                                                    |      |

| 8.2        |            | INIERO GENERAL<br>VORKING PRINCIPLE FOR TIMERO                   |      |

|            | ۷<br>3.2.1 | 8-bit Timer Mode                                                 |      |

|            | 3.2.1      | 8-bit Counter Mode                                               |      |

|            |            | Software Programmable Pre-scaler                                 |      |

|            | 3.2.3      | Software Programmable Pre-scaler.                                |      |

|            | 3.2.4      |                                                                  |      |

|            | 3.2.5      |                                                                  |      |

| 8.3        | I          | IMER0 RELATED REGISTER                                           | . 65 |

| 9. 1       | ΓΙΜΕ       | R1                                                               | 66   |

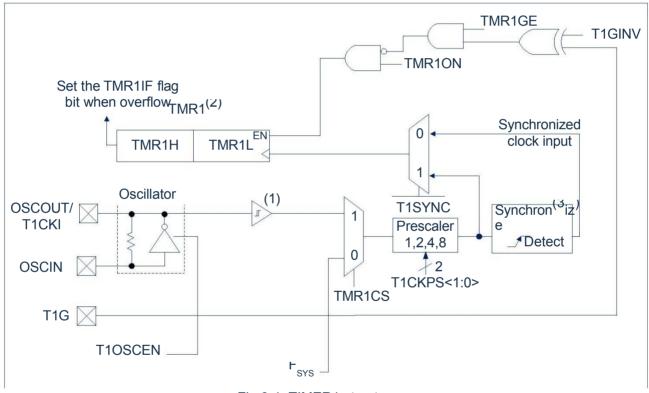

| 9.1        | Т          | IMER1 General                                                    | . 66 |

| 9.2        | V          | Vorking Principle for TIMER1                                     | . 67 |

| 9.3        | C          | CLOCK SOURCE SELECTION                                           | . 67 |

| ç          | 9.3.1      | Internal Clock Source                                            |      |

| ç          | 9.3.2      | External Clock Source                                            |      |

| 9.4        |            | IMER1 Pre-scaler                                                 |      |

| 9.5        |            | IMER1 Oscillator                                                 |      |

| 9.6        |            | IMER1 Working Principle Under Aasynchronous Counter Mode         |      |

|            |            | Read and Write Operations to TIMER1 In Asynchronous Counter Mode |      |

| 9.7        |            | IMER1 GATE CONTROL                                               |      |

|            | -          |                                                                  | -    |

# Cmsemicon<sup>®</sup>

| 9.8    | TIMER1 INTERRUPT                                      | 70 |

|--------|-------------------------------------------------------|----|

| 9.9    | TIMER1 Working Principle During Sleep                 |    |

| 9.10   | TIMER1 CONTROL REGISTER                               | 71 |

| 10 TI  | MER2                                                  | 72 |

|        |                                                       |    |

| 10.1   |                                                       |    |

| 10.2   |                                                       |    |

| 10.3   | TIMER2 RELATED REGISTER                               |    |

| 11. Al | NALOG TO DIGITAL CONVERSION (ADC)                     | 75 |

| 11.1   | ADC GENERAL                                           | 75 |

| 11.2   | ADC CONFIGURATION                                     |    |

|        | 2.1 Port configuration                                |    |

|        | 2.2 Channel selection                                 |    |

|        | 2.3 ADC internal reference voltage                    |    |

|        | 2.4 ADC reference voltage                             |    |

|        | 2.5 Converter clock                                   |    |

|        | 2.6 ADC Interrupt                                     |    |

|        | 2.7 Output Formatting                                 |    |

| 11.3   |                                                       |    |

|        | 3.1 Start conversion                                  |    |

|        | 3.2 Complete conversion                               |    |

|        | 3.3 Stop conversion                                   |    |

|        | 3.4 Working principle of ADC in sleep mode            |    |

|        | 3.5 A/D conversion procedure                          |    |

|        | ADC RELATED REGISTER                                  |    |

| 12. LC | CD DRIVER MOD                                         | 83 |

| 12.1   | LCD FUNCTION ENABLE                                   | 83 |

| 12.2   | LCD RELATED REGISTER                                  | 83 |

| 12.3   | LCD OPERATING INSTRUCTIONS                            | 87 |

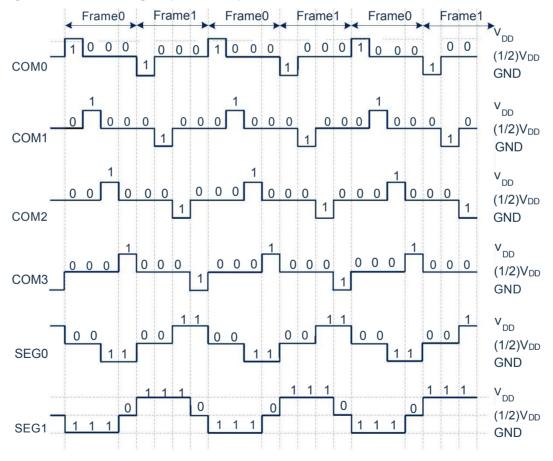

| 12.    | 3.1 1/3 Bias register operation                       | 87 |

| 12.    | 3.2 1/3 Bias timing diagram                           | 87 |

| 12.    | 3.3 1/2 Bias register operation                       | 88 |

| 12.    | 3.4 1/2 Bias timing diagram                           | 88 |

| 13. PV | WM MODE                                               | 89 |

| 13.1   | PIN CONFIGURATION                                     | 89 |

| 13.2   | DESCRIPTION OF RELATED REGISTERS                      |    |

| 13.3   | PWM REGISTER WRITE OPERATION SEQUENCE                 |    |

| 13.4   | PWM Period                                            |    |

| 13.5   | PWM DUTY CYCLE                                        |    |

| 13.6   | SYSTEM CLOCK FREQUENCY CHANGES                        |    |

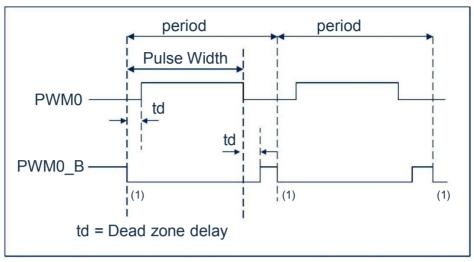

| 13.7   | PROGRAMMABLE DEAD TIME DELAY MODE                     |    |

| 13.8   | PWM settings                                          |    |

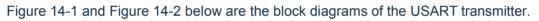

| 14. UN | NIVERSAL SYNCHRONOUS/ASYNCHRONOUS TRANSMITTER (USART) |    |

| 14.1   | USART ASYNCHRONOUS MODE                               |    |

|        | 1.1 USART Asynchronous Generator                      |    |

|        | 1.2 USART Asynchronous Receiver                       |    |

| 14.2   | CLOCK PRECISION FOR ASYNCHRONOUS OPERATIONS           |    |

| 14.3   | USART RELATED REGISTER                                |    |

| 14.4   | USART BAUD RATE GENERATOR (BRG)                       |    |

| 14.5   | USART SYNCHRONOUS MODE                                |    |

|        |                                                       |    |

| 14     | 5.1 Synchronous Master Control Mode                |     |

|--------|----------------------------------------------------|-----|

| 14     | .5.2 Synchronous Slave Mode                        |     |

| 15. PI | ROGRAM EEPROM AND PROGRAM MEMORY CONTROL           |     |

| 15.1   | GENERAL                                            |     |

| 15.2   | RELATED REGISTER                                   |     |

|        | 2.1 EEADR and EEADRH Register                      |     |

| 15     | 5.2.2 EECON1 and EECON2 Register                   |     |

| 15.3   | READ PROGRAM EEPROM                                |     |

| 15.4   | WRITE PROGRAM EEPROM                               |     |

| 15.5   | READ PROGRAM MEMORY                                |     |

| 15.6   | WRITE PROGRAM MEMORY                               |     |

| 15.7   |                                                    |     |

|        | 5.7.1 Programming Time for Program EEPROM          |     |

|        | 5.7.2 The times of programming EEPROM.             |     |

|        | 0.7.3 Write Verification                           |     |

| 15     | 5.7.4 Protection to Avoid Writing Wrongly          |     |

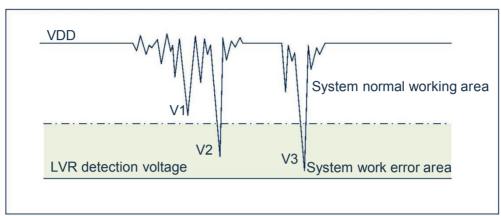

| 16. LC | OW VOLTAGE DETECTION (LVD)                         | 122 |

| 16.1   | LVD MOD GENERAL                                    |     |

| 16.2   | LVD RELATED REGISTER                               |     |

| 16.3   | LVD OPERATION                                      |     |

| 17. EI | LECTRICAL PARAMETERS                               |     |

| 17.1   | LIMIT PARAMETERS                                   |     |

| 17.2   | DC ELECTRICAL CHARACTERISTIC                       |     |

| 17.3   | ADC ELECTRICAL CHARACTERISTIC                      |     |

| 17.4   | ADC INTERNAL LDO REFERENCE VOLTAGE CHARACTERISTICS |     |

| 17.5   | Power-on Reset Features                            |     |

| 17.6   | LVD ELECTRICAL CHARACTERISTIC                      |     |

| 17.7   | ELECTRICAL CHARACTERISTICS                         |     |

| 18. IN | ISTRUCTIONS                                        | 127 |

| 18.1   | INSTRUCTIONS TABLE                                 |     |

| 18.2   | INSTRUCTIONS ILLUSTRATION                          |     |

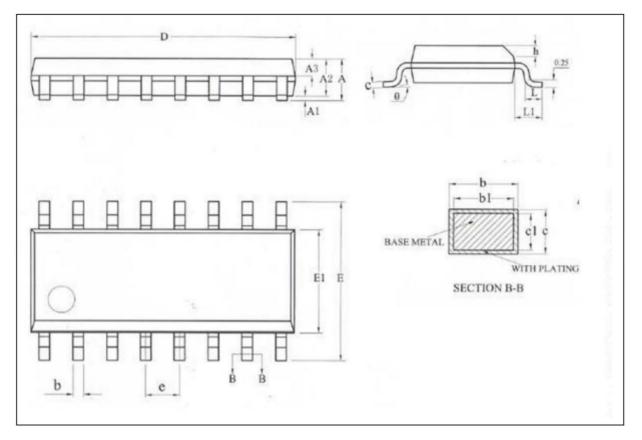

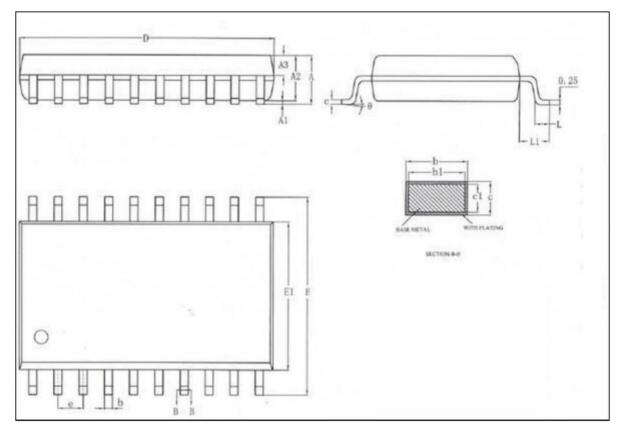

| 19. P/ | ACKAGING                                           |     |

| 19.1   | SOP8                                               |     |

| 19.1   | SOP14                                              |     |

| 19.2   | SOP16                                              |     |

| 19.5   | SOP20                                              |     |

|        |                                                    |     |

| 20. RI | EVISION HISTORY                                    | 150 |

### **1. Product Description**

### 1.1 Features

- Memory

- ROM: 2K×16Bit

- RAM: 256×8Bit

- 8-level stack buffer

- Short and clear command system (68 commands)

- Lookup table function

- Built in WDTtimer

- Interrupt

- 3 timer Interrupt

- RA Interrupt on Change in logic level

- Other external hardware Interrupt

- Timer:

- 8-bit Timer: TIMER0, TIMER2

- 16-bit Timer: TIMER1

- Built in LVD module

- Support multiple voltage: 2.2V/2.4V/2.7V/ 3.0V/ 3.3V/3.7V/4.0V/4.3V

- Built in 128-byte EEPROM

- Rewritable up to 100,000 times

- Voltage range: 2.6V—5.5V@16MHz

1.8V\_5.5V@8MHz

Temperature range: -40°<sub>C</sub>\_85°<sub>C</sub>

- Multiple ways of oscillation

- Internal RC: design frequency of 8MHz/16MHz

- External XT oscillation: up to 8MHz

- Instructions period (single instruction or double instructions)

- Built-in low voltage detection circuit

- USART communication module

- PWM module with complementary output

- 5 channels of PWM, can be set to 2 channels of complementary output

- 4ch PWM with shared period and separated duty cycle

- 1ch PWM with separated period and separated duty cycle

- Built-in LCD driver module

- All I/O ports have optional SEG/ COM output

- All I/O ports can choose 1/2BIAS or 1/3BIAS output

- All I/O port drive currents are optional

- High precision 12-bit ADC

- Built in high presicion 1.2V reference voltage

- ±1.5% @VDD=2.5V~5.5V T<sub>A</sub>=25°C

- ±2% @VDD=2.5V~5.5V T<sub>A</sub>=-40°C~85°C

#### Product comparison: PRODUCT Pro EE ADC USART PACKAGE ROM RAM I/O LCD CMS79F111 2Kx16 256x8 128x8 6 1/2Bias1/3Bias 12Bitx6 SOP8 1 CMS79F112 2Kx16 256x8 128x8 12 1/2Bias1/3Bias 12Bitx12 1 SOP14 12Bitx14 128x8 14 SOP16 CMS79F113 2Kx16 256x8 1/2Bias1/3Bias 1 CMS79F116 128x8 1 SOP20 2Kx16 256x8 18 1/2Bias1/3Bias 12Bitx18

Note: ROM---- Read Only Memory Pro EE---- program EEPROM

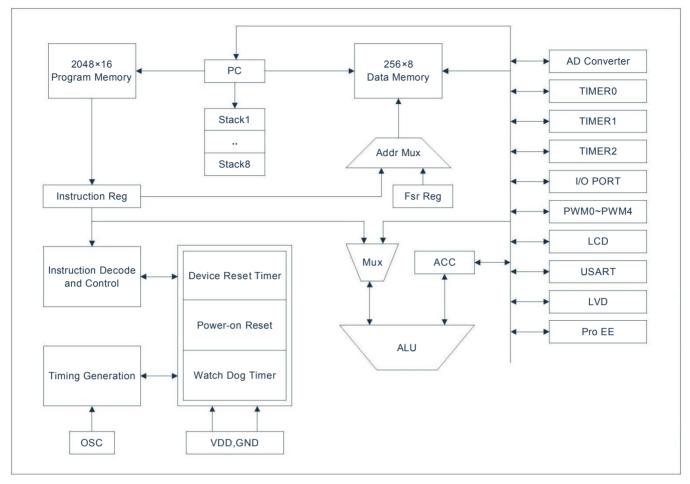

### 1.2 System structure

### **1.3 Pin configuration**

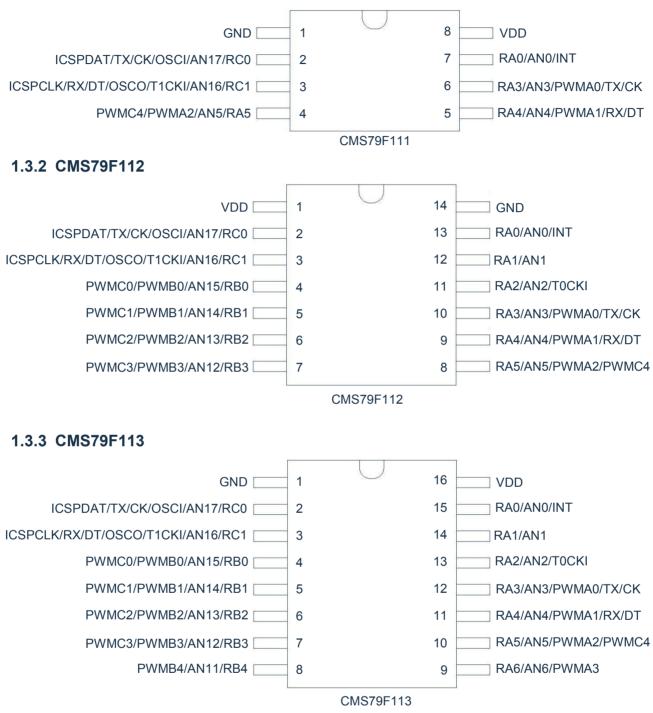

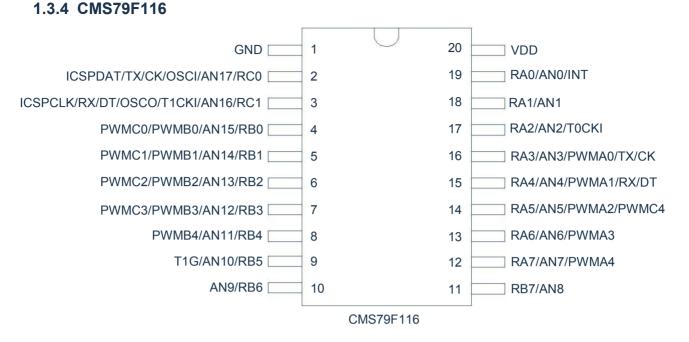

#### 1.3.1 CMS79F111

- Note:

1) The serial port function of RA4 and RA3 and the serial port function of RC0 and RC1 are set by CONFIG.

- 2) The PWMx function is set by the PWMCON1 register.

#### CMS79F11x Pin description and function:

| Pin             | IO                                | Pin description                                                                                                                  |  |

|-----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| VDD, GND        | Р                                 | Power supply voltage input pin, ground pin                                                                                       |  |

| OSCIN/OSCOUT    | I/O                               | Crystal Oscillator Input/Output Pin                                                                                              |  |

| RA0-RA7         | I/O                               | Programmed as input pin or push-pull output pin, with pull-up resistor function and interrupt on change in logic level function  |  |

| RB0-RB7         | I/O                               | Programmed as input pin or push-pull output pin, with pull-up resistor function                                                  |  |

| RC0-RC1         | I/O                               | Programmed as input pin or push-pull output pin, with pull-up resistor function                                                  |  |

| ICSPCLK/ICSKCLK | I/O                               | Programming clock/data pin                                                                                                       |  |

| AN0-AN17        | I                                 | 12-bit ADC input pin                                                                                                             |  |

| ТОСКІ           | I                                 | TIMER0 external clock input pin                                                                                                  |  |

| T1CKI           | I TIMER1 external clock input pin |                                                                                                                                  |  |

| T1G             | I                                 | TIMER1 gate control input pin                                                                                                    |  |

| ТХ/СК           | 0                                 | Asynchronous serial port sending pin/synchronous serial port clock input and output pin (configurable in different IO ports)     |  |

| RX/DT           | I                                 | Asynchronous serial port receiving pin/synchronous serial port data input an<br>output pins (configurable in different IO ports) |  |

| PWMx0-4         | 0                                 | PWM0-4 output function (configurable in different IO ports)                                                                      |  |

| INT             | I                                 | External interrupt input pin                                                                                                     |  |

### 1.4 System Configuration Register

System configuration registor (CONFIG) is MCU's initial condition's ROM choice. It can only be programmed by CMS burner. User cannot visit it or place any action on it. It includes the following.

- 1. OSC (choice of oscillation)

- ♦ INTRC Internal RC oscillation

- ◆ XT External crystal oscillation

- 2. INTRC\_SEL (internal oscillation frequency)

- ◆ INTRC8M F<sub>HSI</sub>choose internal 8MHz RC oscillation

- ◆ INTRC16M F<sub>HSI</sub>choose internal 16MHz RC oscillation

- 3. WDT (watchdog choice)

- ENABLE Enable watchdog timer

- DISABLE

Disable watchdog timer

- 4. PROTECT (encyption)

- DISABLE Disable FLASH code encyption

- ENABLE Enable FLASH code encryption, after which the read value from burning the simulator is uncertain.

- 5. LVR\_SEL (low voltage detection selection)

- 1.8V To select this reset voltage point, Fosc needs to select 8MHz

- ♦ 2.0V

- ♦ 2.6V

- 6. USART\_SEL (TX/RX) (USART port selection)

- RC0/RC1 Select RC0 as TX, RC1 as RX

- ◆ RA3/RA4 Select RA3 as TX □, RA4 as RX

- 7. ICSPPORT\_SEL (simulation port selection)

- ICSP ICSPCLK, DAT port keep as similation port, all functions disabled

- NORMAL ICSPCLK, DAT port as normal port

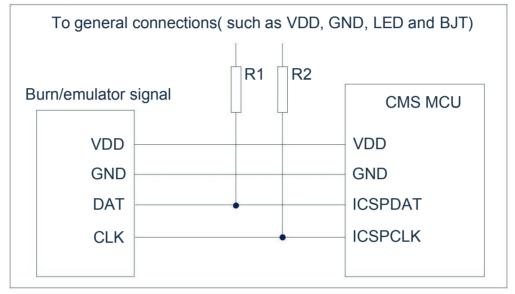

### 1.5 Online Serial Programming

Can perform serial programming on MCU t the final application circuit. Programming is done through the following:

- Power wire

- Ground wire

- Data wire

- Clock wire

This ensures users to use un-programmed devices to make circuit and only program the MCU just before the product being delivered. Therefore, the lastest version of firmware can be burned into the MCU.

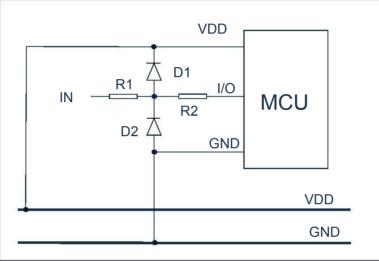

Fig 1-1: Typical connection for online serial programming

In the above figure, R1 and R2 are the electrical isolation devices, normally represented by resistor with the following resistance: R1 $\ge$ 4.7K, R2 $\ge$ 4.7K.

### 2. Central Processing Unit (CPU)

### 2.1 Memory

#### 2.1.1 Program Memory

CMS79F11x program memory space

#### FLASH:2K

| 0000H | Reset Vector               | Program start, jump to user program     |

|-------|----------------------------|-----------------------------------------|

| 0001H |                            |                                         |

| 0002H |                            |                                         |

| 0003H |                            |                                         |

| 0004H | Interrupt vector           | Interrupt entry, user interrupt program |

|       |                            | User program area                       |

|       |                            |                                         |

|       |                            |                                         |

| 7FDH  |                            |                                         |

| 7FEH  |                            |                                         |

| 7FFH  | Jump to Reset Vector 0000H | End of program                          |

|       |                            | 1                                       |

#### 2.1.1.1 Reset Vector (0000H)

MCU has 1-byte long system reset vector (0000H). It has 3 ways to reset:

- Power-on reset

- Watchdog reset

- Low voltage reset (LVR)

When any above reset happens, program will start to execute from 0000H, system registerwill be recovered to default value. PD and TO from STATUS register can determine the which reset is performed from above. The following program illustrayes how to define the reset vector from FLASH.

| ORG | 0000H         | ; system reset vector         |

|-----|---------------|-------------------------------|

| JP  | START         |                               |

| ORG | 0010H         | ; start of user program       |

|     |               |                               |

|     |               | ; user program                |

|     |               |                               |

| END |               | ; program end                 |

|     | JP<br>ORG<br> | JP START<br>ORG 0010H<br><br> |

#### 2.1.1.2 Interrupt Vector

The address for interrupt vector is 0004H. Once the interrupt responds, the current value for program counter PCwill be saved to stack buffer and jump to 0004H to execute interruptservice program. All interruptwill enter 0004H. User will determine which interrupt to execute according to the bit of register of interrupt flag bit. The following program illustrate how to write interrupt service program.

| f          |      | ,     |                          |

|------------|------|-------|--------------------------|

|            | ORG  | 0000H | ; systemresetvector      |

|            | JP   | START |                          |

|            | ORG  | 0004H | ; start of user program  |

| INT_START: |      |       |                          |

|            | CALL | PUSH  | ; save ACC and STATUS    |

|            |      |       | ; user interrupt program |

|            |      |       |                          |

| INT_BACK:  |      |       |                          |

|            | CALL | POP   | ; back to ACC and STATUS |

|            | RETI |       | ; interrupt back         |

| START:     |      |       |                          |

|            |      |       | ; user program           |

|            |      |       |                          |

|            | END  |       | ; program end            |

| ,          |      |       |                          |

Example: define interrupt vector, interrupt program is placed after user program

# Note: MCU does not provide specific unstack and push instructions, so user needs to protect interrupt scene.

#### Example: interrupt-in protection

| PUSH: |            |                            |  |

|-------|------------|----------------------------|--|

| LD    | ACC_BAK,A  | ; save ACC to ACC_BAK      |  |

| SW    | APA STATUS | ; swap half-byte of STATUS |  |

| LD    | STATUS_BA  | K,A ; save to STATUS_BAK   |  |

| RET   | Г          | ; back                     |  |

#### Example: interrupt-out restore

| SWAPR<br>SWAPA | ACC_BAK<br>ACC_BAK | ; swap the half-byte data in ACC_BAK<br>; swap the half-byte data from ACC_BAK to ACC |

|----------------|--------------------|---------------------------------------------------------------------------------------|

| LD             |                    | ; pass the value in ACC to STATUS                                                     |

| POP:<br>SWAPA  | STATUS_BAK         | ; swap the half-byte data from STATUS_BAK to ACC                                      |

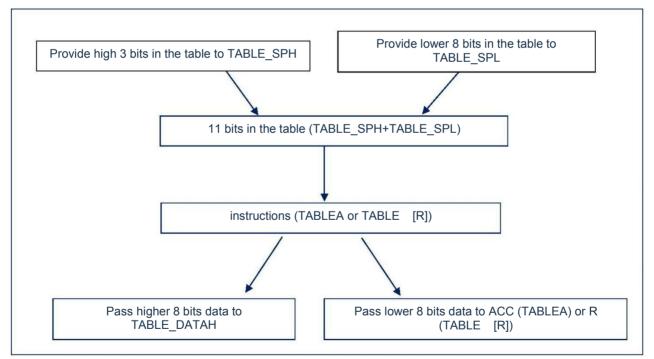

#### 2.1.1.3 Look-up Table

Any address in FLASH can be use as look-up table.

Related instructions:

- TABLE [R] Pass the lower byte in table to register R, pass higher byte to TABLE\_DATAH.

- TABLEA Pass the lower byte in table to ACC, pass higher byte to TABLE\_DATAH.

related register:

- TABLE\_SPH(9AH) Read/write register to indicate higher 3 bits in the table.

- TABLE\_SPL(9BH) Read/write register to indicate lower 8 bits in the table.

- TABLE\_DATAH(94H) Read only register to save higer bit information in the table

Note: Write the table address into TABLE\_SPH and TABLE\_SP before using look-up. If main program and interrupt service programboth use look-up tablein structions, the value for TABLE\_SPH in the main program may change due to the look-up instructions from interrupt and hence cause error. Avoid using look-up table instruction in both main program and interrupt service. Dsiable the interrupt before using the look-up table instruction and enable interrupt after the look-up instructions are done.

Fig 2-1: Flow chart for table usage

#### The following illustrates how to use the table in the program.

|       |               | ;continue from user program                             |

|-------|---------------|---------------------------------------------------------|

| LDIA  | 02H           | ;lower bits address in the table                        |

| LD    | TABLE_SPL,A   |                                                         |

| LDIA  | 06H           | ; higher bits address in the table                      |

| LD    | TABLE_SPH,A   |                                                         |

| TABLE | R01           | ;table instructions, pass the lower 8 bits (56H) to R01 |

| LD    | A,TABLE_DATAH | ;pass the higher 8 bits from look-up table (34H) to ACC |

| LD    | R02,A         | ;pass the value from ACC (34H)to R02                    |

|       |               | ;user program                                           |

|       |               |                                                         |

| ORG   | 0600H         | ;start address of table                                 |

| DW    | 1234H         | ;table content at 0600H                                 |

| DW    | 2345H         | ;table content at 0601H                                 |

| DW    | 3456H         | ;table content at 0602H                                 |

| DW    | 0000H         | ;table content at 0603H                                 |

#### 2.1.1.4 Jump Table

Jump table can achieve multi-address jump feature. Since the addition of PCL and ACC is the new value of PCL, multi-address jump is then achieved through adding different valueof ACC to PCL. If the value of ACC isn, then PCL+ACC represent the current address plus n. After the execcution of the current instructions, the value of PCL will add 1 (refer to the following examples). If PCL+ACC overflows, then PC will not carry. As such, user can achieve multi-address jump through setting different values of ACC.

PCLATH is the PC high bit buffer register. Before operating on PCL, value must be given to PCLATH. Example: correct illustration of multi-address jump

| FLASH address |      |          |                            |  |

|---------------|------|----------|----------------------------|--|

|               | LDIA | 01H      |                            |  |

|               | LD   | PCLATH,A | ;must give value to PCLATH |  |

|               |      |          |                            |  |

| 0110H:        | ADDR | PCL      | ;ACC+PCL                   |  |

| 0111H:        | JP   | LOOP1    | ;ACC=0, jump to LOOP1      |  |

| 0112H:        | JP   | LOOP2    | ;ACC=1, jump to LOOP2      |  |

| 0113H:        | JP   | LOOP3    | ;ACC=2, jump to LOOP3      |  |

| 0114H:        | JP   | LOOP4    | ;ACC=3, jump to LOOP4      |  |

| 0115H:        | JP   | LOOP5    | ;ACC=4, jump to LOOP5      |  |

| 0116H:        | JP   | LOOP6    | ;ACC=5, jump to LOOP6      |  |

|               | -    |          | ,                          |  |

#### Example: wrong illustration of multi-address jump

| FLASH address |      |        |                               |

|---------------|------|--------|-------------------------------|

|               | CLR  | PCLATH |                               |

|               |      |        |                               |

| 00FCH:        | ADDR | PCL    | ;ACC+PCL                      |

| 00FDH:        | JP   | LOOP1  | ;ACC=0, jump to LOOP1         |

| 00FEH:        | JP   | LOOP2  | ;ACC=1, jump to LOOP2         |

| 00FFH:        | JP   | LOOP3  | ;ACC=2, jump to LOOP3         |

| 0100H:        | JP   | LOOP4  | ;ACC=3, jump to 0000H address |

| 0101H:        | JP   | LOOP5  | ;ACC=4, jump to 0001H address |

| 0102H:        | JP   | LOOP6  | ;ACC=5, jump to 0002H address |

Note: Since PCI overflow will not carry to the higher bits, the program cannot be placed at the partition of the FLASH space when using PCL to achieve multi-address jump.

#### 2.1.2 Data Memory

#### List of data memory of CMS79F11x

|           | address |             | address | а           | ddress |             | address |

|-----------|---------|-------------|---------|-------------|--------|-------------|---------|

| INDF      | 00H     | INDF        | 80H     | INDF        | 100H   | INDF        | 180H    |

| TMR0      | 01H     | OPTION REG  | 81H     |             | 101H   |             | 181H    |

| PCL       | 02H     | PCL         | 82H     | PCL         | 102H   | PCL         | 182H    |

| STATUS    | 03H     | STATUS      | 83H     | STATUS      | 103H   | STATUS      | 183H    |

| FSR       | 04H     | FSR         | 84H     | FSR         | 104H   | FSR         | 184H    |

| PORTA     | 05H     | TRISA       | 85H     | PIR1        | 105H   |             | 185H    |

| PORTB     | 06H     | TRISB       | 86H     | PIE1        | 106H   |             | 186H    |

| WPUA      | 07H     | WPDB        | 87H     | PIR2        | 107H   |             | 187H    |

| WPUB      | 08H     | OSCCON      | 88H     | PIE2        | 108H   |             | 188H    |

|           | 09H     | WDTCON      | 89H     |             | 109H   |             | 189H    |

| PCLATH    | 0AH     | PCLATH      | 8AH     | PCLATH      | 10AH   | PCLATH      | 18AH    |

| INTCON    | 0BH     | INTCON      | 8BH     | INTCON      | 10BH   | INTCON      | 18BH    |

|           | 0CH     | EECON1      | 8CH     | TMR1L       | 10CH   |             | 18CH    |

|           | 0DH     | EECON2      | 8DH     | TMR1H       | 10DH   |             | 18DH    |

| PWMD23H   | 0EH     | EEDATAL     | 8EH     | T1CON       | 10EH   |             | 18EH    |

| PWM01DT   | 0FH     | EEDATAH     | 8FH     |             | 10FH   |             | 18FH    |

| PWM23DT   | 10H     | EEADRL      | 90H     | ANSEL0      | 110H   |             | 190H    |

| TMR2      | 11H     | PR2         | 91H     | ANSEL1      | 111H   |             | 191H    |

| T2CON     | 12H     | PORTC       | 92H     | ANSEL2      | 112H   |             | 192H    |

| PWMCON0   | 13H     | TRISC       | 93H     | LCDCON      | 113H   |             | 193H    |

| PWMCON1   | 14H     | TABLE_DATAH | 94H     | CSSEL0      | 114H   |             | 194H    |

| PWMTL     | 15H     | IOCA        | 95H     | CSSEL1      | 115H   |             | 195H    |

| PWMTH     | 16H     | EEADRH      | 96H     | CSSEL2      | 116H   |             | 196H    |

| PWMD0L    | 17H     | WPDA        | 97H     | TXSTA       | 117H   |             | 197H    |

| PWMD1L    | 18H     | WPDC        | 98H     | RCSTA       | 118H   |             | 198H    |

| PWMD2L    | 19H     | WPUC        | 99H     | SPBRG       | 119H   |             | 199H    |

| PWMD3L    | 1AH     | TABLE_SPH   | 9AH     | TXREG       | 11AH   |             | 19AH    |

| PWMD4L    | 1BH     | TABLE_SPL   | 9BH     | RCREG       | 11BH   |             | 19BH    |

| PWMD01H   | 1CH     | ADCON1      | 9CH     | CSEN0       | 11CH   |             | 19CH    |

| PWMCON2   | 1DH     | ADCON0      | 9DH     | CSEN1       | 11DH   |             | 19DH    |

| PWM4TL    | 1EH     | ADRESH      | 9EH     | CSEN2       | 11EH   |             | 19EH    |

|           | 1FH     | ADRESL      | 9FH     | LVDCON      | 11FH   |             | 19FH    |

|           | 20H     |             | A0H     |             | 120H   |             | 1A0H    |

|           |         |             |         |             |        |             | I I     |

|           |         | Universal   |         | Universal   |        |             | I I     |

| Universal |         | register    |         | register    |        |             | I I     |

| register  |         | 80byte      |         | 80byte      |        |             | I I     |

| 96 byte   |         |             |         |             |        |             |         |

| 30 Dyte   | 6FH     |             | EFH     |             | 16FH   |             | 1EFH    |

|           | 70H     | Fast memory | F0H     | Fast memory | 170H   | Fast memory | 1F0H    |

|           |         | spce        |         | space       |        | space       |         |

|           | 7FH     | 70H-7FH     | FFH     | 70H-7FH     | 17FH   | 70H-7FH     | 1FFH    |

| BANK0     |         | BANK1       |         | BANK2       |        | BANK3       |         |

Data memory consists of 512×8 bits. It can be devided into to space: special function register and universal data memory. Most of data memory are able to write/read data, only some data memory are read-only. Special register address is from 00H-1FH, 80-9FH, 100-11FH, 180-18BH.

| 地址         | Summary o<br>名称    | Bit7                 | Bit6                                                       | Bit5                | Bit4        | Bit3          | Bit2            | Bit1             | Bit0            | Reset value |

|------------|--------------------|----------------------|------------------------------------------------------------|---------------------|-------------|---------------|-----------------|------------------|-----------------|-------------|

| 00H        | INDF               | Look-up for          | Look-up for this unit will use FSR, not physical register. |                     |             |               |                 |                  | xxxxxxx         |             |

| 01H        | TMR0               | TIMER0 dat           | a register                                                 |                     |             |               |                 |                  |                 | xxxxxxx     |

| 02H        | PCL                | Lower bit of         | program cou                                                | nter                |             |               |                 |                  |                 | 00000000    |

| 03H        | STATUS             | IRP                  | RP1                                                        | RP0                 | то          | PD            | Z               | DC               | С               | 00011xxx    |

| 04H        | FSR                | memory poir          | nters for indir                                            | ect addressing of o | data memory | s             | ^<br>           |                  | 82<br>81        | XXXXXXXX    |

| 05H        | PORTA              | RA7                  | RA6                                                        | RA5                 | RA4         | RA3           | RA2             | RA1              | RA0             | XXXXXXXX    |

| 06H        | PORTB              | RB7                  | RB6                                                        | RB5                 | RB4         | RB3           | RB2             | RB1              | RB0             | XXXXXXXX    |

| 07H        | WPUA               | WPUA7                | WPUA6                                                      | WPUA5               | WPUA4       | WPUA3         | WPUA2           | WPUA1            | WPUA0           | 00000000    |

| 08H        | WPUB               | WPUB7                | WPUB6                                                      | WPUB5               | WPUB4       | WPUB3         | WPUB2           | WPUB1            | WPUB0           | 00000000    |

| 0AH        | PCLATH             |                      |                                                            |                     |             |               | Write buffer of | higher 3 bits of | program counter | 000         |

| 0BH        | INTCON             | GIE                  | PEIE                                                       | TOIE                | INTE        |               | T0IF            | INTF             |                 | 0000-00-    |

| 0EH        | PWMD23H            | PWMD3[9:8] PWMD[9:8] |                                                            |                     |             |               | /ID[9:8]        | 0000             |                 |             |

| 0FH        | PWM01DT            |                      | PWM01 dead zone delay time                                 |                     |             |               |                 |                  | 000000          |             |

| 10H        | PWM23DT            |                      |                                                            |                     | F           | WM23 dead z   | zone delay time |                  |                 | 000000      |

| 11H        | TMR2               | TIMER2 mo            | d register                                                 |                     |             |               |                 |                  |                 | 00000000    |

| 12H        | T2CON              |                      | TOUTPS<br>3                                                | TOUTPS2             | TOUTPS1     | TOUTPS        | TMR2ON          | T2CKPS1          | T2CKPS0         | -0000000    |

| 4011       | PWMCON0            |                      | -                                                          | 01                  |             | 0<br>PWM3EN   | PWM2EN          | PWM1EN           | PWM0EN          | 00000000    |

| 13H        |                    |                      | CLKDIV[2:                                                  | -                   | PWM4EN      | PVVIVIJEIN    | PVVIVIZEIN      |                  |                 |             |

| 14H        | PWMCON1            | PWMIO_               |                                                            | PWM2DTEN            | PWM0DTEN    |               |                 | 01_1             | DIV[1:0]        | 000000      |

| 15H        | PWMTL<br>PWMTH     | PWM period           | low register                                               | PWM                 | 2410-01     | PWM4T9        | PWM4T8          | PWMT9            | PWMT8           | 00000000    |

| 16H        | PWMD0L             | DWM0 duty            | cycle low reg                                              |                     | 04[9.6]     | P VV IVI4 I 9 | P VVIVI4 I 0    | PWWI             | PVVIVITO        | 000000      |

| 17H        | PWMD0L<br>PWMD1L   |                      | , ,                                                        |                     |             |               |                 |                  |                 | 00000000    |

| 18H        | PWMD1L<br>PWMD2L   |                      | cycle low reg                                              |                     |             |               |                 |                  |                 | 00000000    |

| 19H        |                    |                      |                                                            |                     |             |               |                 |                  |                 | 00000000    |

| 1AH<br>1BH | PWMD3L<br>PWMD4L   |                      | cycle low reg                                              |                     |             |               |                 |                  |                 | 00000000    |

|            |                    |                      |                                                            | PWM                 | 0410-01     |               |                 | DWW              | ID0[9:8]        |             |

| 1CH<br>1DH | PWMD01H<br>PWMCON2 |                      |                                                            |                     | PWM4DIR     | PWM3DI<br>R   | PWM2DIR         | PWM1DIR          | PWM0DIR         | 0000        |

| 1EH        | PWM4TL             | PWM4 perio           | d low registe                                              | r                   | 1           | 1             | 1               | 1                | I.              | 00000000    |

| address | name            | Bit7            | Bit6                | Bit5              | Bit4     | Bit3    | Bit2                    | Bit1             | Bit0       | Reset value |

|---------|-----------------|-----------------|---------------------|-------------------|----------|---------|-------------------------|------------------|------------|-------------|

| 80H     | INDF            | Look-up for thi | is unit will use FS | R, not physical i | egister. |         |                         |                  |            | xxxxxxxx    |

| 81H     | OPTION_R<br>EG  |                 | INTEDG              | TOCS              | TOSE     | PSA     | PS2                     | PS1              | PS0        | -1111011    |

| 82H     | PCL             | Lower bit of pr | ogram counter       |                   |          |         |                         |                  |            | 00000000    |

| 83H     | STATUS          | IRP             | RP1                 | RP0               | то       | PD      | Z                       | DC               | С          | 00011xxx    |

| 84H     | FSR             | memory pointe   | ers for indirect ad | ldressing of data | memory   |         |                         |                  |            | XXXXXXXX    |

| 85H     | TRISA           | TRISA7          | TRISA6              | TRISA5            | TRISA4   | TRISA3  | TRISA2                  | TRISA1           | TRISA0     | 11111111    |

| 86H     | TRISB           | TRISB7          | TRISB6              | TRISB5            | TRISB4   | TRISB3  | TRISB2                  | TRISB1           | TRISB0     | 11111111    |

| 87H     | WPDB            | WPDB7           | WPDB6               | WPDB5             | WPDB4    | WPDB3   | WPDB2                   | WPDB1            | WPDB0      | 00000000    |

| 88H     | OSCCON          |                 | IRCF2               | IRCF1             | IRCF0    |         |                         |                  | SCS        | -1100       |

| 89H     | WDTCON          |                 |                     |                   |          |         |                         |                  | SWDTEN     | 0           |

| 8AH     | PCLATH          |                 |                     |                   |          |         | Write buffer<br>counter | of higher 3 bits | of program | 000         |

| 8BH     | INTCON          | GIE             | PEIE                | T01E              | INTE     |         | T0IF                    | INTF             |            | 0000-00-    |

| 8CH     | EECON1          | EEPGD           |                     | EETIME1           | EETIME0  | WRERR   | WREN                    | WR               | RD         | 0-00x000    |

| 8DH     | EECON2          | EEPROM cont     | trol register 2 (no | t physical addre  | ss)      |         |                         |                  |            |             |

| 8EH     | EEDAT           | EEDAT7          | EEDAT6              | EEDAT5            | EEDAT4   | EEDAT3  | EEDAT2                  | EEDAT1           | EEDAT0     | XXXXXXXX    |

| 8FH     | EEDATH          | EEDATH7         | EEDATH6             | EEDATH5           | EEDATH4  | EEDATH3 | EEDATH<br>2             | EEDATH1          | EEDATH0    | XXXXXXXX    |

| 90H     | EEADR           | EEADR7          | EEADR6              | EEADR5            | EEADR4   | EEADR3  | EEADR2                  | EEADR1           | EEADR0     | 00000000    |

| 91H     | PR2             | TIMER2 period   | d register          |                   |          |         | d                       |                  |            | 00000000    |

| 92H     | PORTC           |                 |                     |                   |          |         |                         | RC1              | RC0        | xx          |

| 93H     | TRISC           |                 |                     |                   |          |         |                         | TRISC1           | TRISC0     | 11          |

| 94H     | TABLE_DA<br>TAH | Table high dat  | a                   |                   |          |         |                         |                  |            | xxxxxxx     |

| 95H     | IOCA            | IOCA7           | IOCA6               | IOCA5             | IOCA4    | IOCA3   | IOCA2                   | IOCA1            | IOCA0      | 00000000    |

| 96H     | EEADRH          |                 |                     |                   |          |         | EEADRH<br>2             | EEADRH1          | EEADRH0    | 000         |

| 97H     | WPDA            | WPDA7           | WPDA6               | WPDA5             | WPDA4    | WPDA3   | WPDA2                   | WPDA1            | WPDA0      | 00000000    |

| 98H     | WPDC            |                 |                     |                   |          |         |                         | WPDC1            | WPDC0      | 00          |

| 99H     | WPUC            |                 |                     |                   |          |         |                         | WPUC1            | WPUC0      | 00          |

| 9AH     | TABLE_SP<br>H   |                 |                     |                   |          |         | Т                       | able high 3 addr | ress       | XXX         |

| 9BH     | TABLE_SP        | Table low poin  | Iter                | 1                 | I        | 1       | 1                       |                  |            | XXXXXXXX    |

| 9CH     | ADCON1          | ADFM            | CHS4                |                   |          |         | LDO_EN                  | LDO_S            | EL[1:0]    | 00000       |

| 9DH     | ADCON0          | ADCS1           | ADCS0               | CHS3              | CHS2     | CHS1    | CHS0                    | GO/              | ADON       | 00000000    |

| 9EH     | ADRESH          | Higher bit of A | /D result register  |                   | ·>       | A.      |                         | DONE             |            | XXXXXXXX    |

| 9FH     | ADRESL          | Lower bit of A/ | D result register   |                   |          |         |                         |                  |            | xxxxxxxx    |

|         | 1      |                 | gisters in e                                   |                 |              | ī        |                             |                     | r       | T           |

|---------|--------|-----------------|------------------------------------------------|-----------------|--------------|----------|-----------------------------|---------------------|---------|-------------|

| address | name   | Bit7            | Bit6                                           | Bit5            | Bit4         | Bit3     | Bit2                        | Bit1                | Bit0    | Reset value |

| 100H    | INDF   | Look-up for thi | s unit will use F                              | SR , not physic | al register. |          |                             |                     |         | xxxxxxx     |

| 102H    | PCL    | Lower bit of pr | ogram counter                                  |                 |              |          |                             |                     |         | 00000000    |

| 103H    | STATUS | IRP             | RP1                                            | RP0             | ТО           | PD       | Z                           | DC                  | С       | 00011xxx    |

| 104H    | FSR    | memory pointe   | ers for indirect a                             | ddressing of da | ata memory   |          |                             |                     |         | XXXXXXXX    |

| 105H    | PIR1   |                 | ADIF                                           | RCIF            | TXIF         |          | PWMIF                       | TMR2IF              | TMR1IF  | -000-000    |

| 106H    | PIE1   |                 | ADIE                                           | RCIE            | TXIE         |          | PWMIE                       | TMR2IE              | TMR1IE  | -000-000    |

| 107H    | PIR2   |                 |                                                |                 | EEIF         |          |                             | RACIF               | LVDIF   | 000         |

| 108H    | PIE2   |                 |                                                |                 | EEIE         |          |                             | RACIE               | LVDIE   | 000         |

| 10AH    | PCLATH |                 |                                                |                 |              |          | Write buffer of I<br>counte | higher 3 bits of pr | ogram   | 000         |

| 10BH    | INTCON | GIE             | PEIE                                           | TOIE            | INTE         |          | T0IF                        | INTF                |         | 0000-00-    |

| 10CH    | TMR1L  | 16-bit TIMER1   | register low byt                               | e data register | •            |          |                             | o                   |         | XXXXXXXX    |

| 10DH    | TMR1H  | 16-bit TIMER1   | 16-bit TIMER1 register high byte data register |                 |              |          | xxxxxxx                     |                     |         |             |

| 10EH    | T1CON  | T1GINV          | TMR1GE                                         | T1CKPS1         | T1CKPS0      | T0OSCEN  | T1SYNC                      | TMR1CS              | TMR10N  | 00000000    |

| 110H    | ANSEL0 | ANS7            | ANS6                                           | ANS5            | ANS4         | ANS3     | ANS2                        | ANS1                | ANS0    | 00000000    |

| 111H    | ANSEL1 | ANS15           | ANS14                                          | ANS13           | ANS12        | ANS11    | ANS10                       | ANS9                | ANS8    | 00000000    |

| 112H    | ANSEL2 |                 |                                                |                 |              |          |                             | ANS17               | ANS16   | 00          |

| 113H    | LCDCON | LCDEN           | FRAME                                          | BIAS            |              |          |                             | LCDISL              | E[1:0]  | 00000       |

| 114H    | CSSEL0 | CS7SEL          | CS6SEL                                         | CS5SEL          | CS4SEL       | CS3SEL   | CS2SEL                      | CS1SEL              | CS0SEL  | 00000000    |

| 115H    | CSSEL1 | CS15SEL         | CS14SEL                                        | CS13SEL         | CS12SEL      | CS11SEL  | CS10SEL                     | CS9SEL              | CS8SEL  | 00000000    |

| 116H    | CSSEL2 |                 |                                                |                 |              |          |                             | CS17SEL             | CS16SEL | 00          |

| 117H    | TXSTA  | CSRC            | TX9EN                                          | TXEN            | SYNC         | SCKP     | STOPBIT                     | TRMT                | TX9D    | 00000010    |

| 118H    | RCSTA  | SPEN            | RX9EN                                          | SREN            | CREN         | RCIDL    | FERR                        | OERR                | RX9D    | 00001000    |

| 119H    | SPBRG  | USART baud      | ate 8-bit registe                              | r               |              |          |                             |                     | un      | 00000000    |

| 11AH    | TXREG  | USART transn    | nit data register                              |                 |              |          |                             |                     |         | 00000000    |

| 11BH    | RCREG  | USART receiv    | e data register                                |                 |              |          |                             | s                   |         | xxxxxxx     |

| 11CH    | CSEN0  | CS7EN           | CS6EN                                          | CS5EN           | CS4EN        | CS3EN    | CS2EN                       | CS1EN               | CS0EN   | 00000000    |

| 11DH    | CSEN1  | CS15EN          | CS14EN                                         | CS13EN          | CS12EN       | CS11EN   | CS10EN                      | CS9EN               | CS8EN   | 00000000    |

| 11EH    | CSEN2  |                 |                                                |                 |              |          |                             | CS17EN              | CS16EN  | 00          |

| 11FH    | LVDCON | LVD_RES         |                                                |                 |              | LVD_SEL2 | LVD_SEL1                    | LVD_SEL0            | LVDEN   | 000000      |

| Address | Name   | Bit7          | Bit6                                                      | Bit5          | Bit4            | Bit3             | Bit2           | Bit1 | Bit0    | Reset value |

|---------|--------|---------------|-----------------------------------------------------------|---------------|-----------------|------------------|----------------|------|---------|-------------|

| 180H    | INDF   | Look-up for t | ok-up for this unit will use FSR , not physical register. |               |                 |                  |                |      | xxxxxxx |             |

| 182H    | PCL    | Lower bit of  | ver bit of program counter (PC)                           |               |                 |                  | 00000000       |      |         |             |

| 183H    | STATUS | IRP           | RP1                                                       | RP0           | то              | PD               | Z              | DC   | С       | 00011xxx    |

| 184H    | FSR    | memory poir   | nters for indirect                                        | addressing of | data memory     |                  |                |      |         | XXXXXXXX    |

| 18AH    | PCLATH |               |                                                           |               | Write buffer of | higher 5 bits of | f program coui | nter |         | 00000       |

| 18BH    | INTCON | GIE           | PEIE                                                      | T01E          | INTE            |                  | T01F           | INTF |         | 0000-00-    |

### 2.2 Addressing Mode

#### 2.2.1 Direct Addressing

Operate on RAM through accumulator (ACC)

Example: pass the value in ACC to 30H register

LD

| Example: | Example: pass the value in 30H register to ACC |       |  |  |  |  |

|----------|------------------------------------------------|-------|--|--|--|--|

|          | LD                                             | А,30Н |  |  |  |  |

30H,A

#### 2.2.2 Immediate Addressing

Pass the immediate value to accumulator (ACC).

Example: pass immediate value 12H to ACC

LDIA 12H

#### 2.2.3 Indirect Addressing

Data memory can be direct or indirect addressing. Direct addressing can be achieved through INDF register, INDF is not physical register. When load/save value in INDF, address is the value in FSR register (lower 8 bits) and IRP bit in STATUS register (9<sup>th</sup> bit), and point to the register of this address. Therefore, after setting the FSR register and the IRP bit of STATUS register, INDF register can be regarded as purpose register. Read INDF (FSR=0) indirectly will produce 00H. Write INDF register indirectly will casue an empty action. The following example shows how indirect addressing works.

Example: application of FSR and INDF

| LDIA | 30H         |                                                                     |

|------|-------------|---------------------------------------------------------------------|

| LD   | FSR,A       | ;Points to 30H for indirect addressing                              |

| CLRB | STATUS, IRP | ;clear the 9 <sup>th</sup> bit of pointer                           |

| CLR  | INDF        | ;clear INDF, which mean clear the 30H address RAM tha FSR points to |

Example: clear RAM (20H-7FH) for indirect addressing:

|       | LDIA | 1FH         |                                        |

|-------|------|-------------|----------------------------------------|

|       | LD   | FSR,A       | ;Points to 1FH for indirect addressing |

|       | CLRB | STATUS, IRP |                                        |

| LOOP: |      |             |                                        |

|       | INCR | FSR         | ;address add 1, initial address is 30H |

|       | CLR  | INDF        | ;clear the address where FSR points to |

|       | LDIA | 7FH         |                                        |

|       | SUBA | FSR         |                                        |

|       | SNZB | STATUS,C    | ;clear until the address of FSR is 7FH |

|       | JP   | LOOP        |                                        |

|       |      |             |                                        |

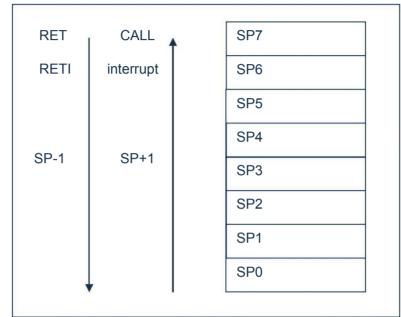

### 2.3 Stack

Stack buffer of the chip has 8 levels. Stack buffer is not part of data memorynor program memory. It cannot be written nor read. Operation on stack buffer is through stack pointers, which also cannot be written nor read. After system resets, SP points to the top of the stack. When sub-program happens or interrupts happens, value in program counter (PC)will be transferred to stack buffer. When return from interrupt or return from sub-program, value is transferred back to PC. The following digram illustrates its working principle.

Fig 2-2: stack buffer working principle

Stack bufferwill follow one principle: 'first in last out'.

Note: stackbuffer has only 8 levels, if the stack is full and interrupt happens which can not be screened out, then only the indication bit of the interrupt will be noted down. The response for the interrupt will be suppressed until the pointer of stack starts to decrease. This feature can prevent overflow of the stack caused by interrupt. Similarly, when stack is full and sub-program happens, then stack will overflow and the contents which enter the stack first will be lost, only the last 8 return address will be saved.

### 2.4 Accumulator (ACC)

#### 2.4.1 General

ALU is the 8-bit arithmetic-logic unit. All math and logic related calculations in MCU are done by ALU. It can perform addition, subtraction, shift and logical calculation on data; ALU can also control STATUS to represent the status of the product of the calculation.

ACC register is an 8-bit register to store the product of calculation of ALU. It does not belong to data memory. It is in CPU and used by ALU during calculation. Hence it cannot be addressed. It can only be used through the instructions provided.

#### 2.4.2 ACC Applications

Example: use ACC for data transfer

| LD | A,R01 | ;pass the value in register R01 to ACC |  |

|----|-------|----------------------------------------|--|

| LD | R02,A | ;pass the value in ACC to register R02 |  |

#### Example: use ACC for immediate addressing

| LDIA  | 30H | ;load the ACC as 30H                                                               |

|-------|-----|------------------------------------------------------------------------------------|

| ANDIA | 30H | ;run 'AND' between value in ACC and immediate number<br>30H,save the result in ACC |

| XORIA | 30H | ; run 'XOR' between value in ACC and immediate number 30H,save the result in ACC   |

Example: use ACC as the first operand of the double operand instructions

| HSUBA | R01 | ;ACC-R01, save the result in ACC |  |

|-------|-----|----------------------------------|--|

| HSUBR | R01 | ;ACC-R01, save the result in R01 |  |

#### Example: use ACC as the second operand of the double operand instructions

| · · · |     | ·                                 |

|-------|-----|-----------------------------------|

| SUBA  | R01 | ;R01-ACC, save the result in ACC  |

| SUBR  | R01 | ; R01-ACC, save the result in R01 |

#### **Program Status Register (STATUS)** 2.5

STATUS register includes:

- status of ALU.

- Reset status.

- Selection bit of Data memory (GPR and SFR)

Just like other registers, STATUS register can be the target register of any other instruction. If A instructions that affects Z, DC or C bit that use STATUS as target register, then it cannot write on these 3 status bits. These bits are cleared or set to 1 according to device logic. TO and PD bit also cabbot be written. Hence the instructions which use STATUS as target instruction may not result in what is predicted.

For example, CLRSTATUS will clear higher 3 bits and set the Z bit to 1. Hence the value of STATUS will be 000u u1uu (u will not change.). Hence, it is recommended to only use CLRB, SETB, SWAPA and SWAPR instructions to change STATUS register because these will not affect any status bits.

| p 9         | J        | ( -         | - /             | 807             |                | 201           |      |      |

|-------------|----------|-------------|-----------------|-----------------|----------------|---------------|------|------|

| 03H         | Bit7     | Bit6        | Bit5            | Bit4            | Bit3           | Bit2          | Bit1 | Bit0 |

| STATUS      | IRP      | RP1         | RP0             | ТО              | PD             | Z             | DC   | С    |

| Read/write  | R/W      | R/W         | R/W             | R/W             | R/W            | R/W           | R/W  | R/W  |

| Reset value | 0        | 0           | 0               | 1               | 1              | Х             | Х    | Х    |

| •           | •        |             |                 |                 |                |               |      |      |

| Bit7        | IRP:     | Selection   | bit of registe  | er memory (f    | or indirect ac | ldressing)    |      |      |

|             | 1=       |             | d Bank3 (10     |                 |                | 0/            |      |      |

|             | 0=       |             | d Bank1 (00     |                 |                |               |      |      |

| Bit6~Bit5   | RP[1:0]: |             | bit of memo     | ,               |                |               |      |      |

|             | 00:      | Select Ba   | ink 0;          |                 |                |               |      |      |

|             | 01:      | Select Ba   | ink 1;          |                 |                |               |      |      |

|             | 10:      | Select Ba   | ink 2;          |                 |                |               |      |      |

|             | 11:      | Select Ba   | ink 3.          |                 |                |               |      |      |

| Bit4        | TO:      | Time out    | bit;            |                 |                |               |      |      |

|             | 1=       | Power on    | or CLRWD        | T instructions  | s or STOP in   | structions;   |      |      |

|             | 0=       | WDT time    | e out.          |                 |                |               |      |      |

| Bit3        | PD:      | Power do    | wn;             |                 |                |               |      |      |

|             | 1=       | Power on    | or CLRWD        | T instructions  | s;             |               |      |      |

|             | 0=       | STOP ins    | tructions.      |                 |                |               |      |      |

| Bit2        | Z:       | Bit for res | ult inzero;     |                 |                |               |      |      |

|             | 1=       | The resul   | t of arithmeti  | ic or logical o | operation is z | ero;          |      |      |

|             | 0=       | The resul   | t of an arithn  | netic or logic  | al operation   | is not zero.  |      |      |

| Bit1        | DC:      | Half Carr   | y/Borrow Bit;   |                 |                |               |      |      |

|             | 1=       | The fourt   | n low bit of th | ne result is c  | arried to the  | high bit;     |      |      |

|             | 0=       | The fourt   | n low bit of th | ne result did   | not carry to   | the high bit. |      |      |

| Bit0        | C:       | Carry/bor   |                 |                 |                |               |      |      |

|             | 1=       | •           |                 | result has a    |                |               |      |      |

|             | 0=       | The highe   | est bit of the  | result is not   | carried.       |               |      |      |

|             |          |             |                 |                 |                |               |      |      |

program status register STATUS (03H)

TO and PD bit can reflect the reason for reset of chip. The following is the events which affects the TO and PD and the status of TO nad PD after these events.

| events                 | ТО | PD |

|------------------------|----|----|

| Power on               | 1  | 1  |

| WDT overflow           | 0  | Х  |

| STOP instructions      | 1  | 0  |

| CLRWDT<br>instructions | 1  | 1  |

| sleep                  | 1  | 0  |

| ТО | PD | Reset reason                  |

|----|----|-------------------------------|

| 0  | 0  | WDT overflow awaken MCU       |

| 0  | 1  | WDT overflow non-sleep status |

| 1  | 1  | Power on                      |

TO/PD status after reset

Events which affect TO/PD

### 2.6 Pre-scaler (OPTION\_REG)

OPTION\_REG registercan be read or written. Each control bit for configuration is as follow:

- TIMER0/WDT pre-scaler.

- ◆ TIMER0.

#### pre-scaler OPTION\_REG(81H)

|             |      |        | · · · · · · · · · · · · · · · · · · · | <u></u> |      |      |      |      |

|-------------|------|--------|---------------------------------------|---------|------|------|------|------|

| 81H         | Bit7 | Bit6   | Bit5                                  | Bit4    | Bit3 | Bit2 | Bit1 | Bit0 |

| OPTION_REG  | -    | INTEDG | TOCS                                  | T0SE    | PSA  | PS2  | PS1  | PS0  |

| Read/write  | -    | R/W    | R/W                                   | R/W     | R/W  | R/W  | R/W  | R/W  |

| Reset value | -    | 1      | 1                                     | 1       | 1    | 0    | 1    | 1    |

| Bit7      | Unused   |                                                          |                                          |            |                              |                     |  |  |  |

|-----------|----------|----------------------------------------------------------|------------------------------------------|------------|------------------------------|---------------------|--|--|--|

| Bit6      | INTEDG:  | Edge selection bit for triggering interrupt              |                                          |            |                              |                     |  |  |  |

|           | 1=       | INT pin rising edge triggered interrupt                  |                                          |            |                              |                     |  |  |  |

|           | 0=       | INT pi                                                   | INT pin falling edge triggered interrupt |            |                              |                     |  |  |  |

| Bit5      | T0CS:    | Selec                                                    | tion bit                                 | for TIME   | R0 clock source.             |                     |  |  |  |

|           | 0=       | Intern                                                   | al instru                                | uctions p  | eriod clock (Fsys/4).        |                     |  |  |  |

|           | 1=       | transi                                                   | tion edg                                 | ge on TOO  | CKI pin                      |                     |  |  |  |

| Bit4      | T0SE:    | Edge                                                     | selectio                                 | on bit for | TIMER0 clock source          |                     |  |  |  |

|           | 0=       | Increa                                                   | ase whe                                  | en TOCKI   | pin signal transite from low | v to high           |  |  |  |

|           | 1=       | Increase when T0CKI pin signal transite from high to low |                                          |            |                              |                     |  |  |  |

| Bit3      | PSA:     | pre-scaler allocation                                    |                                          |            |                              |                     |  |  |  |

|           | 0=       | pre-so                                                   | aler all                                 | ocates to  | TIMER0 mod                   |                     |  |  |  |

|           | 1=       | pre-so                                                   | caler all                                | ocates to  | WDT                          |                     |  |  |  |

| Bit2~Bit0 | PS2~PS0: | config                                                   | uration                                  | bit for pr | e-allocation parameters.     |                     |  |  |  |

|           |          | PS2                                                      | PS1                                      | PS0        | TMR0 frequency ratio         | WDT frequency ratio |  |  |  |

|           |          | 0                                                        | 0                                        | 0          | 1:2                          | 1:1                 |  |  |  |

|           |          | 0                                                        | 0                                        | 1          | 1:4                          | 1:2                 |  |  |  |

|           |          | 0                                                        | 1                                        | 0          | 1:8                          | 1:4                 |  |  |  |

|           |          | 0                                                        | 1                                        | 1          | 1:16                         | 1:8                 |  |  |  |

|           |          | 1                                                        | 0                                        | 0          | 1:32                         | 1:16                |  |  |  |

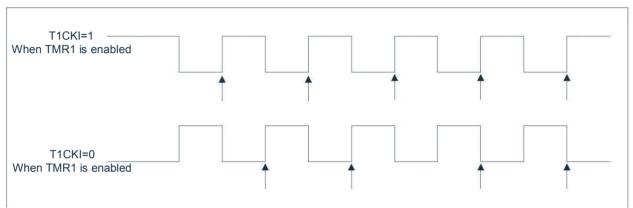

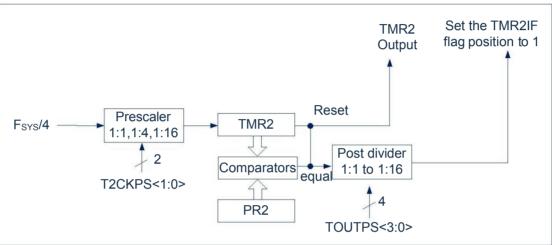

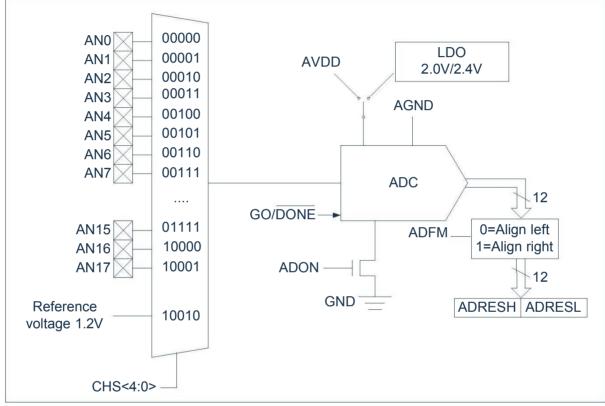

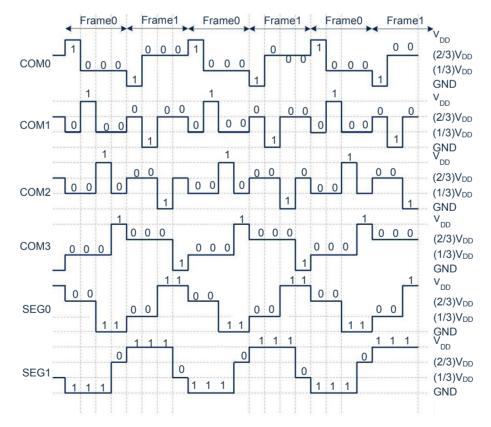

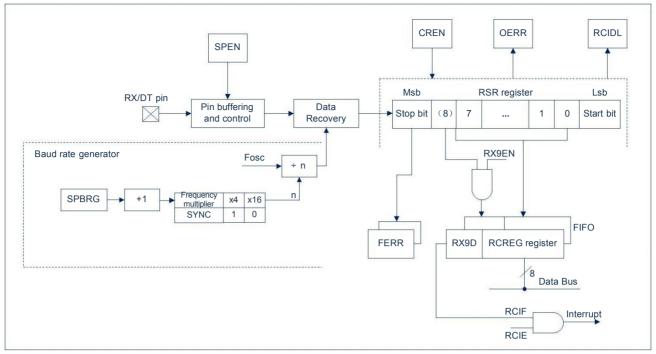

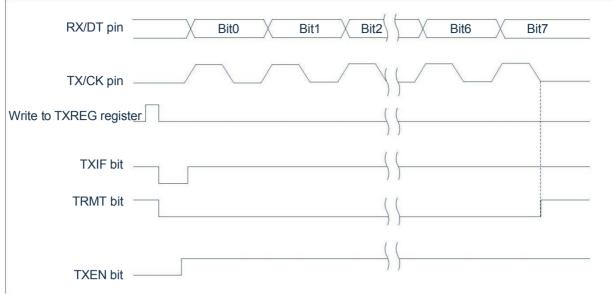

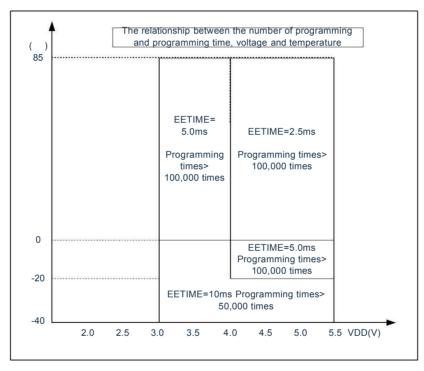

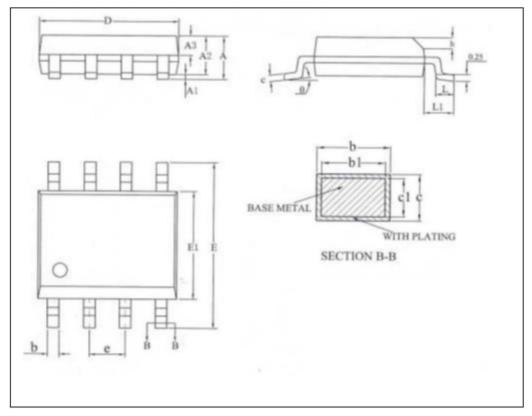

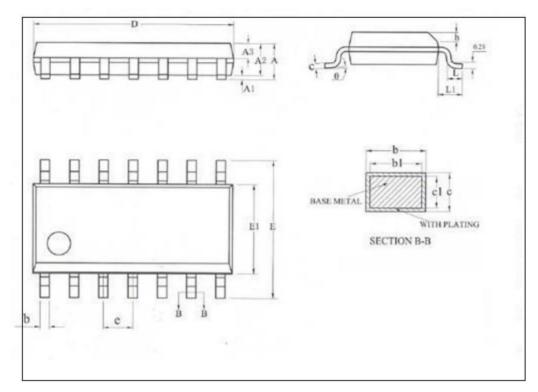

|           |          | 1                                                        | 0                                        | 1          | 1:64                         | 1:32                |  |  |  |