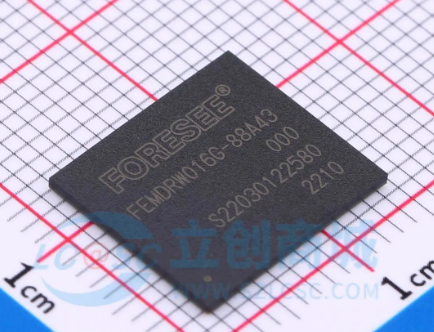

Compatible with MCS-51 1T Instruction System

System clock frequency supports up to 48MHz

Machine cycle maximum 1TSYS @ FSYS≤24MHz

Machine cycle maximum 2TSYS@ FSYS=48MHz

Memory

Program FLASH:16K×8Bit

Data FLASH:1K×8Bit

General RAM: 256×8Bit

Universal XRAM: 1K×8Bit

Program FLASH supports partition protection

4 Oscillation Modes

HSI-Internal high-speed oscillator: 48MHz

HSE-External high-speed oscillator: 8MHz/16MHz

LSE-External low-speed oscillator: 32.768KHz

LSI-Internal low-speed oscillator: 125KHz

Low-voltage Reset Function (LVR)

1.8V/2.0V/2.5V/3.5V

Low-voltage Detection Function (LVD)

2.0V/2.2V/2.4V/2.7V/3.0V/3.7V/4.0V/4.3V

GPIO

Up to 22 GPIOs

All digital functions can be assigned to any GPIO

Support pull-up/down resistor function

Support edge (rising edge/falling edge/both edge)interrupt

Support wake-up function

Interrupt Source

Support all external port interrupts

Up to 7 timer interrupts

Other peripheral interrupts

Timers

WDT/WWDT timer (watchdog/ window watchdogtimer)

Up to 5 timers: Timer0/1, Timer2, Timer3/4

LSE Timer (support sleep wake function)

WUT (wake-up timer)

BRT/ BRT1 (baud rate clock generation timer)

Communication Module

1xSPI (communication rate up to 6Mb/s)

1xI2C (communication rate up to 400Kb/s)

Up to 2xUART (baud rate up to 1Mb/s)

Low Power Mode

Idle mode (IDLE)

Sleep mode (STOP,Power consumption approximation 6uA)

Operating Voltage Range

2.1V~5.5V

Operating Temperature Range

-40℃~105℃

Buzzer Driver

50% duty cycle, frequency can be set freely

Enhanced PWM

6 channels enhanced PWM

6 independent cycle counters

Support independent /complementary/ synchronous/group mode

Support edge alignment/center alignment

Support complementary mode dead zone delayfunction

Support mask function and fault protectionfunction

High-precision 12-bit ADC

All GPIOs (22I/Os) support AD channels

Optional reference voltage (1.2V/2.0V/2.4V/3.0V/VDD)

Can detect internal 1.2V reference voltage

Support hardware trigger start conversion function

Support a set of result digital comparison function

Two analog comparators(ACMP0/1)

6 options for the positive terminal, internal - 1.2V/VDD divider for the negative terminal

Comparator supports unilateral/bilateral hysteresis

Optional hysteresis voltage 10/20/60mV

Support comparison output trigger EPWM brakeGPIO port

The internal 1.2V/VDD divider of the negativeterminal can be connected to the internal ADCchannel

Two operational amplifiers (OP0/1)

Three terminals of each op amp are multiplexed with GPIO port

The positive end supports internal 1.2V input

Support two modes of op amp/comparator

The op-amp output can be connected to the internal ADC channel

The output of the op amp can be connected to the input of the internal analog comparator

Support offset voltage software adjustment

Programmable gain amplifier (PGA)

Support offset voltage software adjustment

Sampling hold circuit (for use with ADC)

Multistage gain optional (1/2/4/8/16/32/64/128x)

Single-ended/pseudo-differential input is supported

The PGA output can be connected to the internal ADC channel

The PGA output can be connected to the internal analog comparator input

Support 96-bit Unique ID Number (UID)

Each chip has an independent ID number

Support Two-wire Serial Programming andDebugging

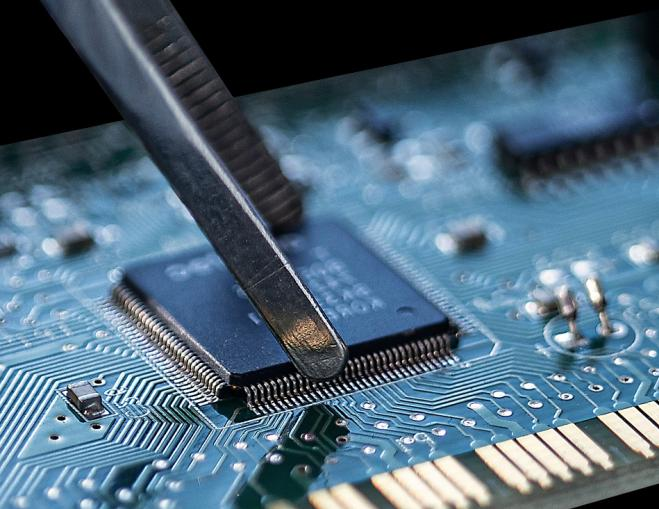

MCU Solutions

MCU Solutions PCBA Solutions

PCBA Solutions Bluetooth Solutions

Bluetooth Solutions

FAQ

FAQ Contact Us

Contact Us

Company News

Company News Technology News

Technology News Industry News

Industry News PCBA News

PCBA News

Company Profile

Company Profile Certificates

Certificates Terms & Conditions

Terms & Conditions Privacy Statement

Privacy Statement

Home Appliances

Home Appliances Beauty Appliances

Beauty Appliances Lighting

Lighting Kid's Toys

Kid's Toys Security Alarm

Security Alarm Health Care

Health Care