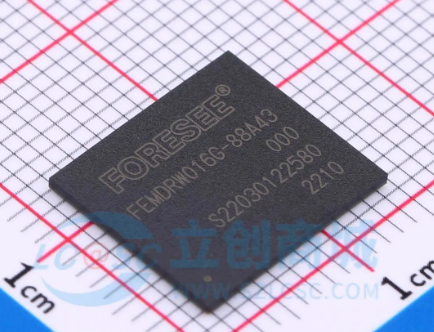

Fully compatible with standard 8051 instruction set

48MHz maximum operating frequency

Machine cycle maximum 1TSYS @ FSYS≤24MHz

Machine cycle maximum 2TSYS @ FSYS=48MHz

Memories

Program FLASH:64K×8Bit

Data FLASH:1K×8Bit

IRAM:256×8Bit

XRAM:4K×8Bit

Program FLASH supports partition protection and IAPfunctions

4 oscillation modes

HSI-Internal high-speed oscillator: 48MHz

HSE-External high-speed crystal oscillator: 8MHz/16MHz

LSE-External low speed crystal oscillator:32.768KHz

LSI-Internal low speed oscillator:125KHz

GPIO

Up to 46 GPIOs

All pins support up/down resistor function

Interrupts generated on rising, falling, or both edges

Support wake up from idle and sleep mode

Interrupts

All external port interrupts

7 timers interrupts

Other peripheral interrupts

Timers

WDT(Watchdog timer)

Timer0/1,Timer2,Timer3/4

LSE Timer(Support wake up)

WUT(wake-up timer)

BRT/ BRT1(Baud rate clock generation timer)

Cyclic redundancy check unit

CRC16(CRC16-CCITT)

Multiplication and division operation unit (MDU)

Support 32bit/16bit, 16bit/16bit, 16bit×16bit

Buzzer Driver

50% duty, frequency can be set freely

Enhanced PWM

Up to 6 channels

Up to 6 independent period counters

Independent/complementary/synchronous/group mode

Edge alignment / center alignment

Dead time delay @complementary mode

Communications

1xSPI(up to 6Mb/s)

1xI2C(up to 400Kb/s)

4xUART(up to 1Mb/s)

Two-Wire Serial Programming And Debugging

Operating Voltage

2.1V~5.5V

Operating Temperature

-40℃~105℃

Low Voltage Reset(LVR)

1.8V/2.0V/2.5V/3.5V

Low Voltage Detection(LVD)

16 levels optional from 2.0V to 4.6V

12-bit ADC

Up to 23 AD external channels

Reference voltage(1.2V/2.0V/2.4V/3.0V/VDD)

Internal 1.2V bandgap as input

Hardware trigger conversion

Conversion results to digital comparison

Hardware LCD driver

The duty cycle can be selected 1/4, 1/5, 1/6, 1/8

Optional LSI/LSE/system clock three clock sources

Traditional resistive LCD, optional 1/2, 1/3, 1/4 BIAS

Support work in sleep mode

Support energy-saving mode, the total resistance of voltage divider can be 60K/225K/900K

Support up to 4COM x 36SEG, 5COM x 35SEG, 6COMx 34SEG, 8COM x 32SEG

Hardware LED driver

Duty cycle can be selected 1/4, 1/5, 1/6, 1/8standards

Support two modes:

Common cathode/common yang

Optional LSI/LSE/system clock three clock sources

COM, SEG current optional

Support up to 4COM x 28SEG、5COM x 27SEG, 6COM x 26SEG、8COM x 24SEG

Two analog comparators (ACMP0/1, offset voltage is less than 1mV)

5 options for the positive terminal, internal 1.2V/VDD divider for the negative terminal

Comparator supports unilateral/bilateral hysteresis

The internal 1.2V/VDD divider of the negative terminal can be connected to the internal ADC channel

Two operational amplifiers (OP0/1, offset voltage is less than 1mV)

Three terminals of each op amp are multiplexed with GPIO port

The positive end supports internal 1.2V input

Support two modes of op amp/comparator

The output of the op amp can be connected to the input of the internal analog comparator

Low Power Mode

Idle mode

Sleep mode

96 Bits Unique Identifier (UID)

Each chip has an independent Identifier

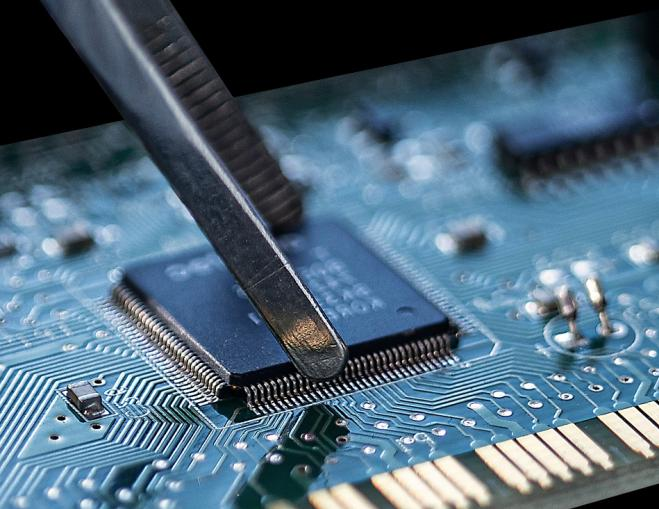

MCU Solutions

MCU Solutions PCBA Solutions

PCBA Solutions Bluetooth Solutions

Bluetooth Solutions

FAQ

FAQ Contact Us

Contact Us

Company News

Company News Technology News

Technology News Industry News

Industry News PCBA News

PCBA News

Company Profile

Company Profile Certificates

Certificates Terms & Conditions

Terms & Conditions Privacy Statement

Privacy Statement

Home Appliances

Home Appliances Beauty Appliances

Beauty Appliances Lighting

Lighting Kid's Toys

Kid's Toys Security Alarm

Security Alarm Health Care

Health Care